ASIC Driver Commands on Cisco IOS XR Software

show controllers plim asic spa bay

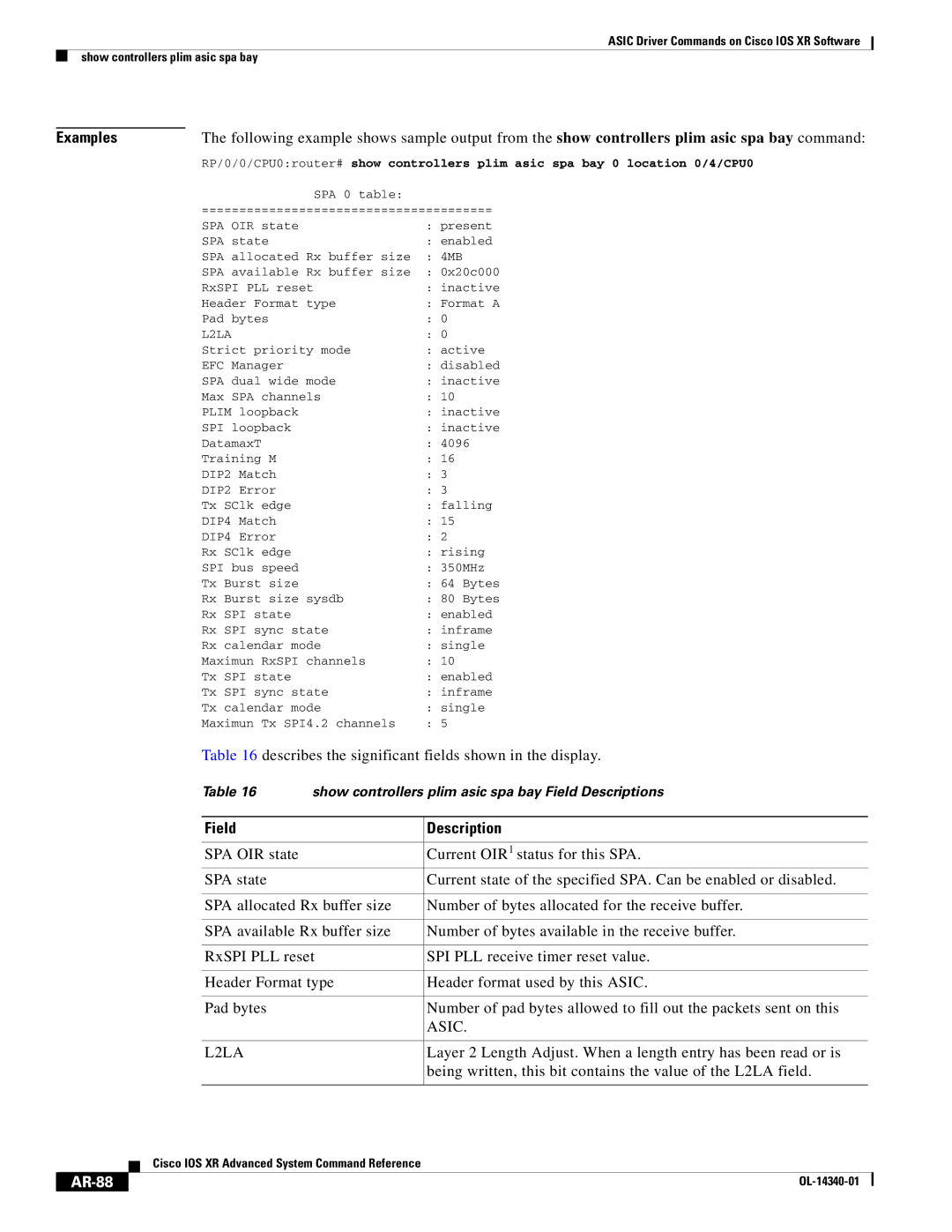

Examples | The following example shows sample output from the show controllers plim asic spa bay command: | ||

| RP/0/0/CPU0:router# show controllers plim asic spa bay 0 location 0/4/CPU0 | ||

|

| SPA 0 table: |

|

| ======================================= | ||

| SPA OIR state |

| : present |

| SPA state |

| : enabled |

| SPA allocated Rx buffer size | : 4MB | |

| SPA available Rx buffer size | : 0x20c000 | |

| RxSPI PLL reset | : inactive | |

| Header Format type | : Format A | |

| Pad bytes |

| : 0 |

| L2LA |

| : 0 |

| Strict priority mode | : active | |

| EFC Manager |

| : disabled |

| SPA dual wide mode | : inactive | |

| Max SPA channels | : 10 | |

| PLIM loopback |

| : inactive |

| SPI loopback |

| : inactive |

| DatamaxT |

| : 4096 |

| Training M |

| : 16 |

| DIP2 Match |

| : 3 |

| DIP2 Error |

| : 3 |

| Tx SClk edge |

| : falling |

| DIP4 Match |

| : 15 |

| DIP4 Error |

| : 2 |

| Rx SClk edge |

| : rising |

| SPI bus speed |

| : 350MHz |

| Tx Burst size |

| : 64 Bytes |

| Rx Burst size sysdb | : 80 Bytes | |

| Rx SPI state |

| : enabled |

| Rx SPI sync state | : inframe | |

| Rx calendar mode | : single | |

| Maximun RxSPI channels | : 10 | |

| Tx SPI state |

| : enabled |

| Tx SPI sync state | : inframe | |

| Tx calendar mode | : single | |

| Maximun Tx SPI4.2 channels | : 5 | |

| Table 16 describes the significant fields shown in the display. | ||

| Table 16 | show controllers plim asic spa bay Field Descriptions | |

|

|

|

|

| Field |

| Description |

|

|

|

|

| SPA OIR state |

| Current OIR1 status for this SPA. |

| SPA state |

| Current state of the specified SPA. Can be enabled or disabled. |

|

|

| |

| SPA allocated Rx buffer size | Number of bytes allocated for the receive buffer. | |

|

|

| |

| SPA available Rx buffer size | Number of bytes available in the receive buffer. | |

|

|

| |

| RxSPI PLL reset | SPI PLL receive timer reset value. | |

|

|

| |

| Header Format type | Header format used by this ASIC. | |

|

|

|

|

| Pad bytes |

| Number of pad bytes allowed to fill out the packets sent on this |

|

|

| ASIC. |

|

|

|

|

| L2LA |

| Layer 2 Length Adjust. When a length entry has been read or is |

|

|

| being written, this bit contains the value of the L2LA field. |

|

|

|

|

| Cisco IOS XR Advanced System Command Reference |

|