ASIC Driver Commands on Cisco IOS XR Software

show controllers cpuctrl ports

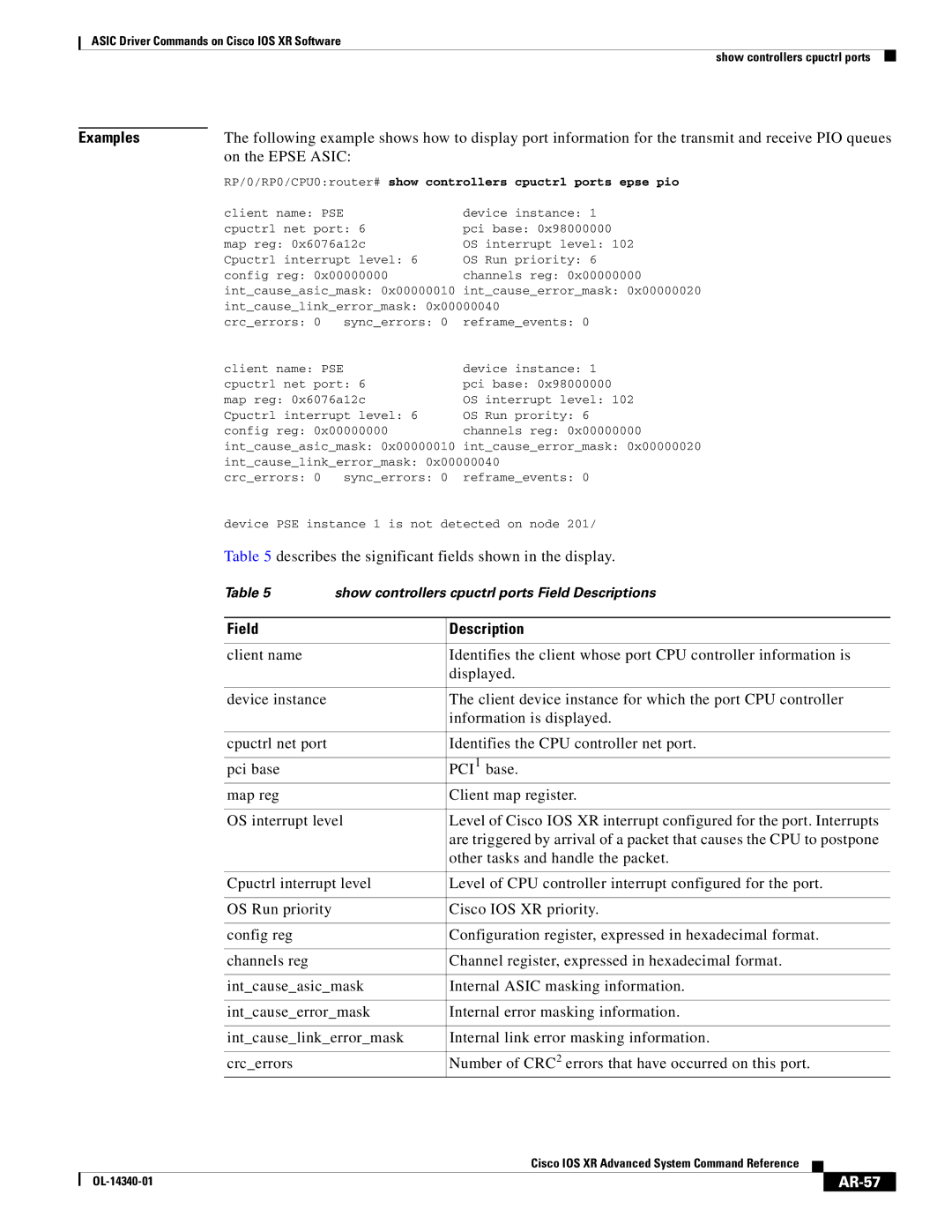

Examples | The following example shows how to display port information for the transmit and receive PIO queues | ||||

| on the EPSE ASIC: |

|

| ||

| RP/0/RP0/CPU0:router# show controllers cpuctrl ports epse pio | ||||

| client name: PSE | device instance: 1 | |||

| cpuctrl net port: 6 | pci base: 0x98000000 | |||

| map reg: 0x6076a12c | OS interrupt level: 102 | |||

| Cpuctrl interrupt level: 6 | OS Run priority: 6 | |||

| config reg: 0x00000000 | channels reg: 0x00000000 | |||

| int_cause_asic_mask: 0x00000010 int_cause_error_mask: 0x00000020 | ||||

| int_cause_link_error_mask: 0x00000040 | ||||

| crc_errors: 0 | sync_errors: 0 | reframe_events: 0 | ||

| client name: PSE | device instance: 1 | |||

| cpuctrl net port: 6 | pci base: 0x98000000 | |||

| map reg: 0x6076a12c | OS interrupt level: 102 | |||

| Cpuctrl interrupt level: 6 | OS Run prority: 6 | |||

| config reg: 0x00000000 | channels reg: 0x00000000 | |||

| int_cause_asic_mask: 0x00000010 int_cause_error_mask: 0x00000020 | ||||

| int_cause_link_error_mask: 0x00000040 | ||||

| crc_errors: 0 | sync_errors: 0 | reframe_events: 0 | ||

| device PSE instance 1 is not detected on node 201/ | ||||

| Table 5 describes the significant fields shown in the display. | ||||

| Table 5 | show controllers cpuctrl ports Field Descriptions | |||

|

|

|

|

|

|

| Field |

|

| Description | |

|

|

|

|

|

|

| client name |

|

| Identifies the client whose port CPU controller information is | |

|

|

|

| displayed. | |

|

|

|

|

|

|

| device instance |

|

| The client device instance for which the port CPU controller | |

|

|

|

| information is displayed. | |

|

|

|

|

|

|

| cpuctrl net port |

|

| Identifies the CPU controller net port. | |

|

|

|

|

|

|

| pci base |

|

| PCI1 base. | |

| map reg |

|

| Client map register. | |

|

|

|

|

| |

| OS interrupt level |

| Level of Cisco IOS XR interrupt configured for the port. Interrupts | ||

|

|

|

| are triggered by arrival of a packet that causes the CPU to postpone | |

|

|

|

| other tasks and handle the packet. | |

|

|

|

|

| |

| Cpuctrl interrupt level |

| Level of CPU controller interrupt configured for the port. | ||

|

|

|

|

|

|

| OS Run priority |

|

| Cisco IOS XR priority. | |

|

|

|

|

|

|

| config reg |

|

| Configuration register, expressed in hexadecimal format. | |

|

|

|

|

|

|

| channels reg |

|

| Channel register, expressed in hexadecimal format. | |

|

|

|

|

| |

| int_cause_asic_mask |

| Internal ASIC masking information. | ||

|

|

|

|

| |

| int_cause_error_mask |

| Internal error masking information. | ||

|

|

|

|

| |

| int_cause_link_error_mask |

| Internal link error masking information. | ||

|

|

|

|

|

|

| crc_errors |

|

| Number of CRC2 errors that have occurred on this port. |

|

|

| Cisco IOS XR Advanced System Command Reference |

|

|

|

|

|

| |||

|

|

|

|

| |

|

|

|

|