HP Caliper User Guide

Copyright 2014 Hewlett-Packard Development Company, L.P

Contents

HP Caliper Options

HP Caliper Measurement Configuration Files

Contents

Using the HP Caliper Advisor in the GUI

Using the HP Caliper Advisor

Configuring HP Caliper

Controlling the Content of Reports 105

Producing a Sampled Call Stack Profile Analysis 134

Producing a Sampled Call Graph Profile Analysis 122

Descriptions of Measurement Reports 171

Contents

Metrics for Integrity Servers Itanium 2 Systems 211

Event Set Descriptions for CPU Metrics HP-UX only 232

Systems 211

212

Glossary 268 Index 273

HP secure development lifecycle

About This Document

Typographic Conventions

Command

Computer output

File name

Related Documents

HP Encourages Your Questions

What is HP Caliper?

What is HP Caliper?

HP Caliper at a Glance

HP Caliper at a Glance

HP Caliper Components User Interfaces

Supported Hardware and Operating Systems

What Does HP Caliper Run On?

Supported Compilers and Application Environments

What Does HP Caliper Run On?

Summary of HP Caliper Features

Getting Started with the HP Caliper Command-Line Interface

Cpucycles

Getting Started with the HP Caliper Command-Line Interface

Target

Getting Started with the HP Caliper Command-Line Interface

Example Adding Instructions to an fprof Report

Example Adding Instructions to an fprof Report

Getting Started with the HP Caliper Command-Line Interface

Global Measurement

Types of Measurements

Sampled Measurements

Precise Measurements

Syntax for caliper Command

What to Look for in Using HP Caliper

Caliper measurement caliperoptions program programarguments

Measurement

Starting HP Caliper

Basic Tasks a Quick Reference

Stopping HP Caliper

Showing HP Caliper Options

Restrictions on Using HP Caliper

Using the HP Caliper Advisor

Creating a Text Report for Analysis

Creating a Report Based on Your Collected Data

Getting Information About HP Caliper

Additional HP Caliper Commands

Caliper info

Caliper report merge diff

Getting Started with the HP Caliper GUI

What Is the HP Caliper GUI?

Window Basics

Getting Started with the HP Caliper GUI

Window Basics

Projects View

Projects View

Collect View

Collect View

Analyze View

Analyze View

Advisor View

Advisor View

Console View

Help View

Diagnostics View

Hints on How to Make Measurements

Tips for Using Views

Making Measurements

Making Measurements

Exploring Performance Data

Getting Performance Tuning Advice

Starting the GUI

Getting Help

Native Local GUI

Remote GUI

Login Screen

Measurement Configuration Files Provided with HP Caliper

HP Caliper Measurement Configuration Files

Ecount

Dtlb

Fprof

Icache

Overview Measurement

Overview Measurement

Location of Measurement Configuration Files

Specifying Option Values in Measurement Configuration Files

Simultaneous fprof Sampling on Multiple PMU Counters

See Hierarchy for Processing an Option Value p

Location of Measurement Configuration Files

Basic Information About Options

HP Caliper Options

Multiple Ways to Specify HP Caliper Option Values

Examples

Or --duration

Or --database

Hierarchy for Processing an Option Value

Examples

Or -?

Or --options-file

Or --help

Or --metrics

Cpuevent

Or --output-file

Or --report-details

Or --process

For PMU Histogram Reports

For Function Coverage Reports

Speriod Srate ,variation ,cpuevent

Or --sampling-spec

Rate

Variation

Or --version

Advice-classes

CPUCYCLES,10000,10%

Branchevent

Advice-details

Advice-cutoff

Analysis-focus

Branch-sampling-spec

Callpath-cutoff

Bus-speed

Bus-speed int

Callpath-cutoffpercentcutoff,cumpercentcutoff,mincount

Cpu-aggregation

Context-lines

Cpu-counter

Cpu-details

Database

Dcache-data-profile

Dcache-hits

Dcache-stores

Debug-file-path=

Db-save

Description-details

Details

Etb-freeze-delay

Duration

Example

Event-defaults privilege-level-mask=levelthreshold=int

Event-defaults

Etb-walkback-cycles

Etb-walkback-cycles integer

Exclude-idle

Exclude-caliper

Fold

Frame-depth

Help

Hotpaths

Ibrp

Inlines

Info

Join

Jre

Latency-buckets

Kernel-stack

Measure-on-interrupts

Memory-usage=

Metrics

Module-default

Module-exclude

Module-include

Noinlines

Module-search-path

Omr

Module-search-path directorydirectory

Output-file

Options-file

Overflow-block

Per-module-data

Process-cutoff

Process

See -p or --process p

Process-cutoffpercentcutoff,cumpercentcutoff,mincount

Report

Read-init-file

Report-details

Rule-files

Psetid psetid

Using --scope system for System-Wide Measurements

Skip-functions

Search

Sort-by

Sort-bymetric,cpuevent

Stop-functions

Source-path-map

Summary-cutoff

Summary-cutoffpercentcutoff,cumpercentcutoff,mincount

System-model Linux only

Sw-process-list=

System-usage=

System-modelmodel-number,number-of-cells

Term-display

Threads

Traps-reported

User-regions

User-regions defaultrum-sum

Version

Rum and sum

What Is the HP Caliper Advisor?

Using the HP Caliper Advisor

Example of an HP Caliper Advisor Report

Limitations to Keep in Mind

Steps in Using the Advisor

Using the HP Caliper Advisor

Example 1 HP Caliper Advisor Report

Command line is

Command Line to Invoke the Advisor

Where adviseoptions are

Command Line to Invoke the Advisor

Advice-cutoff

Advice-classes

Advice-details

Max-count

Getting Started with the Advisor Examples

Simplest Example

More Typical Examples

Explanation of Report Output

Followed by

Then, run the Advisor on the composite performance data

How to Read an Advisor Report

How to Read an Advisor Report

Suggestions for Using the HP Caliper Advisor

How the HP Caliper Advisor Works

How the HP Caliper Advisor Works

Basic Steps in Using the HP Caliper Advisor in the GUI

Using the HP Caliper Advisor in the GUI

Using the HP Caliper Advisor in the GUI

Making Performance Measurement Runs

Selecting Performance Data to Analyze Optional

Selecting Performance Data to Analyze Optional

Projects View, with a Single Project Selected

Generating Advice

Generating Advice

HP Caliper GUI Advisor Menu

Reviewing and Acting on the Advice

Advisor Report in the HP Caliper GUI

Reviewing and Acting on the Advice

Configuring HP Caliper

Configuring HP Caliper

Example of a .caliperinit File

Caliperinit file, you can then simply type

Disasmtargetnamelimit = limit

Setting Constants in the .caliperinit File

Suppressinitwarnings = TrueFalse

Suppressstatementdata = TrueFalse

Configuring Data Collection

Specifying Which CPU Events to Measure

Shortening CPU Event Names

Module-default Module-include Module-exclude

Default Settings for Load Module Data Collection

Specifying Which Load Modules to Collect Data For

Module-include modulelist

How to Specify Load Module Names

Specifying Processes to Measure

Controlling Granularity of Data Collection and Reports

Process Tree Report

For more information, see -s or --sampling-spec p

Syntax for -p Option

Default

Root-forks

Customfunctionname

Using -p some

Glob1glob2

Someopt1,opt2,...pattern

Using HP Caliper in Testing and Quality Assurance

Using HP Caliper in Your Build Process

Examples of the -p Option

Process Origin Options Used with -p some

Using HP Caliper to Generate Test Suite Reports

Attaching to a Running Process to Perform Measurements

Caliper measurement options pid pid

Options for the caliper info Command

Or --cpu-counter

Ccounternamekeywordall

Or --details

Examples of the caliper info Command

Or --output-file

Or --report

HP Caliper Environment Variables

Controlling the Content of Reports

Layout of an HP Caliper Text or CSV Report

Layout of an HP Caliper Text or CSV Report

Metrics You Can Use for Report Sorting and Cutoffs

Controlling the Content of Reports

Metrics You Can Use for Report Sorting and Cutoffs

Available Metrics for Report Sorting and Cutoffs

Module-Centric Reports

For example, assume that you perform this HP Caliper run

This produces a report similar to this truncated report

Process Summary

Process Summary for a --group-by none Run

Process Summary for a Diff Run

Disassembly Listing

Function Details

Function Details

Source Position Correlation

Branch Targets in Disassembly Listings

Address Types Shown

Source Line Data

VSE Information Shown in Report Output

How Functions Are Named in Reports

Unnamed Functions

Unknown Functions

Controlling the Content of Reports

How HP Caliper Saves Data in Databases

Changing the Default Name and Location

Names and Locations for the Databases

Or simply

Creating Reports from Multiple Databases

You can use the caliper report merge diff command to

Caliper report merge diff reportoptions databases

Database2 database1 for caliper diff

Caliper report reportoptions database

Caliper merge reportoptions database1 database2

Creating Reports from Multiple Databases

Cpucycles

Example 2 Example of a caliper merge Run

Caliper diff reportoptions database2 database1

Pmutrace Scgprof

Example 3 Example of a caliper diff Run

Cstack Pmutrace Scgprof

Example of How to Use the caliper diff Command

As cc1 ld

As cc1

How Sampled Call Graph Profile Analysis Works

Producing a Sampled Call Graph Profile Analysis

Differences Between scgprof and cgprof

Producing a Sampled Call Graph Profile Analysis

Sampled Call Graph Text Report Example

Running the HP Caliper Sampled Call Graph Profile

Caliper scgprof caliperoptions program programarguments

Running the HP Caliper Sampled Call Graph Profile

Sampled Call Graph Text Report Example

Sampled Call Graph Text Report Example

Producing a Sampled Call Graph Profile Analysis

Br.cond.dpnt.many self+0x2db0

Producing a Sampled Call Graph Profile Analysis

Sampled Call Graph Text Report Example

Producing a Sampled Call Graph Profile Analysis

Root

Flat Profile Part of the Report

Sampled Call Graph Profile Report Details

Call Graph Part of the Report

Hot Call Paths Part of the Report

Diagnostic Messages appear at the end of the report

Diagnostic Messages

Gprof Fallacy and Possibly Misleading Results

Gprof Fallacy and Possibly Misleading Results

Running HP Caliper to Produce a Call Stack Profile

Producing a Sampled Call Stack Profile Analysis

Call Stack Profile Text Report Example for HP-UX

Caliper cstack caliperoptions program programarguments

Call Stack Profile Text Report Example for HP-UX

Call Stack Profile Text Report Example

Producing a Sampled Call Stack Profile Analysis

Call Stack Profile Text Report Example for HP-UX

Root

Call Stack Profile Text Report Example for HP-UX

Producing a Sampled Call Stack Profile Analysis

Function Indexes Thread 6065598@startroutine Name

An example report for HP Caliper on Linux is shown here

Call Stack Profile Text Report Example for Linux

Call Stack Profile Text Report Example for Linux

Call Stack Profile Text Report Example for Linux

Producing a Sampled Call Stack Profile Analysis

Root

Producing a Sampled Call Stack Profile Analysis

Call Stack Profile Text Report Example for Linux

Producing a Sampled Call Stack Profile Analysis

Blocking Primitives Summary Part of the Report

Call Stack Profile Report Details

Samples-running HP-UX only Samples-blocked HP-UX only

Call Stack Profile Report Details

Example 4 Sample cstack Report Blocking Primitives Details

Avoids gprof Fallacy

Limitations to Using cstack

Pstack like functionality

Sample report follows

Producing a Sampled Call Stack Profile Analysis

153

Performing CPU Metrics Analysis

Measuring Memory Usage Concurrently with Other Measurements

HP Caliper Features Specific to HP-UX

Some examples of the option follow

Examples of the --memory-usage= Option

Memory-usage=all

Memory-usage=beginend

How to Read the Reports

System Memory Configuration Table

Example Report Output

Process Memory Usage Table

Measuring System Usage Concurrently with Other Measurements

Measuring System Usage Concurrently with Other Measurements

Example System Usage Report Output

Caliper measurement options pid

Interpreting the Data

Triggering PMU Samples in Specific Code Regions

Taking PMU Samples in Your Code

Run ./myprog and find the process ID of the process

Taking PMU Samples in Your Code

162 shows part of the resulting report

Precautions When Using Triggered Samples

Restricting PMU Measurements to Specific Code Regions

Caliperpmuenable

Restricting PMU Measurement to Specific Code

Documentation feedback

Documentation feedback

Error #28 Caliper Invalid Measurement Combination

HP Caliper Diagnostic and Warning Messages

Error #28 Caliper Invalid Measurement Combination

Instructions Labeled Stub

Mispredicted Branches Example

HP Caliper Diagnostic and Warning Messages

PMU Sample Hits Outside Function Range

Scgprof Reports Require Kernel Patch

PMU Sample Hits Outside Function Range

HP Caliper Diagnostic and Warning Messages

Example Command Line for CSV Report

Example Command Line for Text Report

Descriptions of Measurement Reports

Alat Measurement Report Description

Metrics for Integrity Servers Itanium 2 Systems

INSTFAILEDCHKALDCALAT.FP

INSTCHKALDCALAT.INT

Alatentryreplaced

Alat Measurement Report Metrics

Alatstorehit

See

How Alat Metrics Are Obtained

Branch Measurement Report Description

Branch Metrics Summed for Entire Run

BRMISPREDDETAIL.ALL.CORRECTPRED

BEFLUSHBUBBLE.ALL

BRMISPREDDETAIL.ALL.WRONGTARGET

BRMISPREDDETAIL.IPREL.CORRECTPRED

BRMISPREDDETAIL.IPREL.WRONGPATH

BRPREDDETAIL.IPRELWRONGPATH

BRPREDDETAIL.IPRELCORRPRED

Number of IP-relative branch types with mispredicted path

BRPREDDETAIL.IPRELWRONGTARGET

BRPREDDETAIL.RETURNWRONGPATH

BRPREDDETAIL.NONRETINDCORRPRED

BRPREDDETAIL.NONRETINDWRONGTARGET

BRPREDDETAIL.RETURNCORRPRED

Information in branch Measurement Reports

Branch Measurement Report Metrics

How branch Metrics Are Obtained

Cgprof Report Description

HP Caliper Call Graph Profile Results Accuracy

Available only on HP-UX

Information in cgprof Measurement Report Fields Flat Profile

Call Graph Profile Metrics

Information in cgprof Measurement Report Parent Listings

Information in cgprof Measurement Report Children Listings

Cpu Measurement Report Description

CPU Event Sets

Example Command Lines for Text Report

L2dcache

L2dcache,l2icache

L2icache

L3cache

Cstack Measurement Report Metrics

Cstack Measurement Report Description

Column Description HP-UX only

Be resolved to a symbol

HP-UX only Sample Hits Waiting

Sample Hits Blocked

Column Run + Block Hits HP-UX only

Cycles Measurement Report Description

Parent Func Hits

Children

Cycles Metrics Summed for Entire Run

BERSEBUBBLE.ALL CPUCPLCHANGES.ALL CPUOPCYCLES.ALL

Retiredinstnop

CYCBEBUBBLE.ANY

CYCBEDETREPLAY.GRLOAD

CYCBEWB2FLUSH.ANY CYCBEIBDSTALL.ANY CYCBEIBDSTALL.GRLOAD

Cycles Measurement Metrics

From that bundle are split issued

How cycles Metrics Are Obtained

Information in cycles Measurement Reports

Dcache Measurement Report Description

Dcache Measurement Report Description

L1DREADS

Dcache Metrics Summed for Entire Run

L1DREADMISSES.ALL

Datareferences

Bubbles, or partial replays

RAW or WAW dependency condition of the instruction

To RAW hazard in an instructions GR load

Dcache Measurement Report Metrics

Information in dcache Measurement Reports

Source statement Instruction

Example dcache Reports

Dcache Measurement Report Description

How Data Cache Metrics Are Obtained

How Latency Bucket Metrics Are Obtained

Dtlb Measurement Report Description

How the Data Summary Information Is Obtained

Dtlb Measurement Report Description

L2DTLBMISSES

Dtlb Metrics Summed for Entire Run

Dtlbinsertshpw

L2DTLBMISSES / Datareferences

FLDTLBLOADMISS.ANY

IA64INSTRETIRED L1DTLBTRANSFER L1DREADS L2DTLBMISSES

FLDTLBINSREQ.NONRETIRED

FLDTLBINSREQ.RETIRED

DTLBHPWREQBLKMISS.FAIL

Dtlb Measurement Report Metrics

L2 Dtlb

HPW

Information in dtlb Measurement Reports

How Data TLB Metrics Are Obtained

Ecount Measurement Report Description

Ecount Metrics Summed for Entire Run

Cpucycles

Ecount Measurement Report Description

Only on HP-UX

Fcount Measurement Report Description

Fcount Measurement Report Metrics

Fcover Measurement Report Description

Fcover Measurement Report Metrics

Information in fcount Measurement Reports

Unknown Source Files

Fprof Measurement Report Description

Directory

Function

BERSEBUBBLE.ALL

Fprof Metrics Summed for Entire Run

Number of CPU cycles spent in WB2 Write back

CYCBEWB2FLUSH.ANY

Flushing of instructions

Dispersal without issuing instructions

Fprof Measurement Metrics

Information in fprof Measurement Reports

How fprof Metrics Are Obtained

Icache Metrics Summed for Entire Run

Icache Measurement Report Description

L1IREADS

L2INSTDEMANDREADS

L2IPREFETCHES

L2IDEMANDREADS

L2IREADS.ALL.ALL

L2IREADS.MISS.ALL

L1 instruction cache misses per

Information in icache Measurement Reports

Icache Measurement Report Metrics

Function Details

Itlb Measurement Report Description

How Instruction Cache Metrics Are Obtained

Itlb Measurement Report Description

ITLBMISSESFETCH.L1ITLB

Itlb Metrics Summed for Entire Run

ITLBMISSESFETCH.L2ITLB

BELOSTBWDUETOFE.ALL

Flitlbmiss

L1ITLBINSERTSHPW L1IREADS

Mlitlbmiss

Mlitlbhpwaborts

Flitlbinserthpw

Itlb Measurement Report Metrics

Cycles lost due to branch execution

Information in itlb Measurement Reports

Column Description Itlb L2 Fill

How Instruction TLB Metrics Are Obtained

Itlb HPW Fill

Itlb Soft Fill

Pmutrace Measurement Report Description

Scgprof Measurement Report Description

Scgprof Measurement Report Metrics Flat Profile

Scgprof Measurement Report Metrics Call Graph Profile

Is profiled otherwise blank

Scgprof Measurement Report Description

Information in scgprof Measurement Report Children Listings

Information in scgprof Measurement Report Parent Listings

Column Description Call Total

Column Description

Traps Measurement Report Description

Traps Metrics Summed for Entire Run

Cycles lost due to RSE stalls

Cycles lost due to pipeline-flush stalls

Information in traps Measurement Reports

Traps Measurement Metrics

How traps Metrics Are Obtained

Brpath Event Set

Event Set Descriptions for CPU Metrics

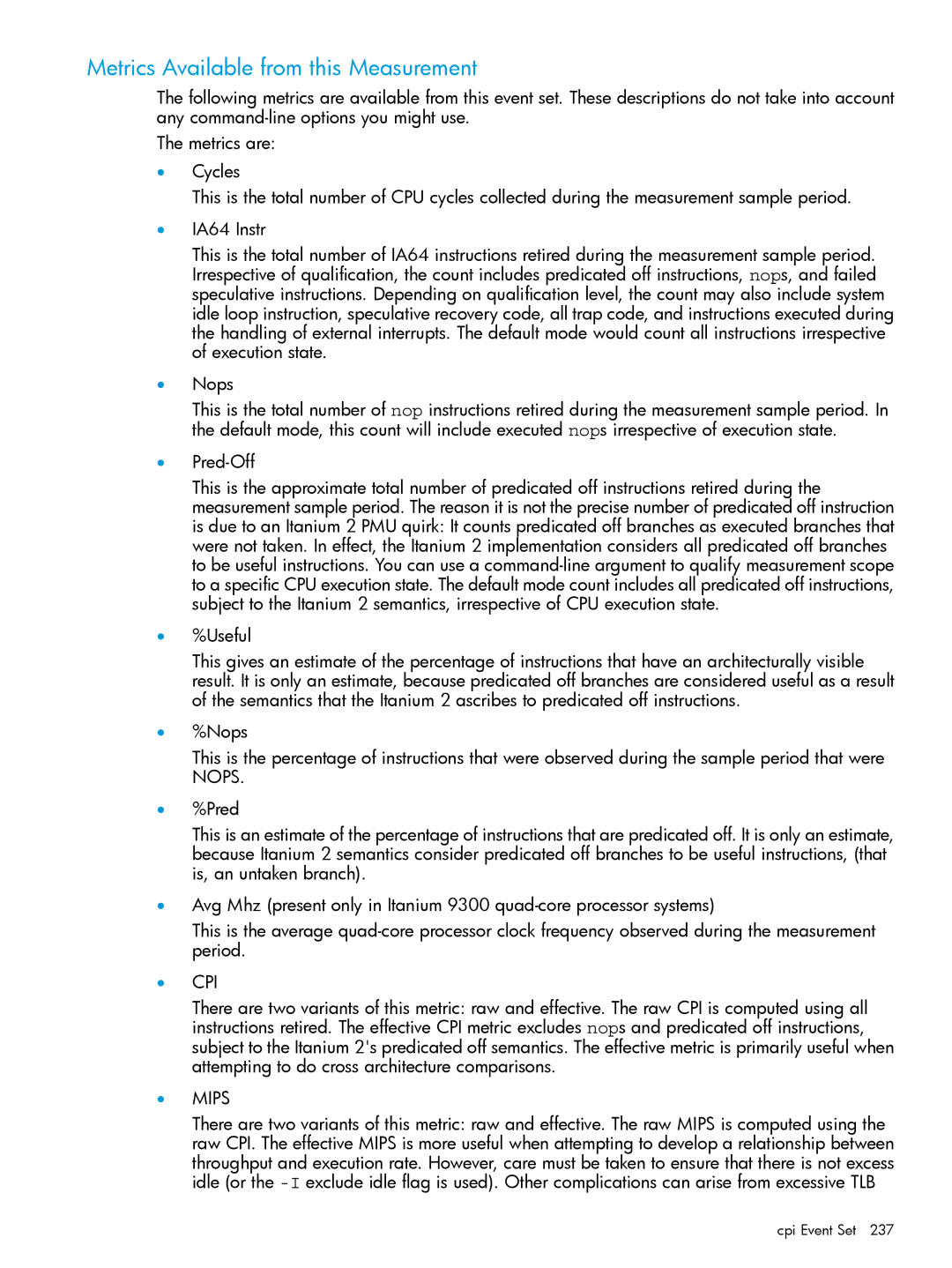

Metrics Available from this Measurement

Include idle --exclude-idle False

Brpred Event Set

Brpred Event Set

Iprel

C2c Event Set

C2c Event Set

Cpi Event Set

CPI

Pred-Off

Mips

Cpi Event Set

Available only on Itanium 2 and dual-core Itanium 2 systems

Cpubus Event Set

Cspec Event Set

Cspec Event Set

Dispersal Event Set

Dspec Event Set

Dspec Event Set

Metrics Available from this Measurement

FCVT.fx

Fp Event Set

SIR

L1dcache Event Set

L1dcache Event Set

NON RSE Misses per Kinst

L1icache Event Set

L1icache Event Set

L2cache Event Set

L2cache Event Set

L2dcache Event Set

L2icache Event Set

L2icache Event Set

Metrics Available from this Measurement

L3cache Event Set

L3cache Event Set

Event Set Descriptions for CPU Metrics

Memreq Event Set

Metrics Available for Intel Itanium 9500 series systems

Memreq Event Set

Queues Event Set

Queues Event Set

Snoop Event Set

Stall Event Set

Replay Event Set

Include idle --exclude-idle False

Metrics Available for Intel Itanium 9500 series systems

Sysbus Event Set

Dcache

Sysbus Event Set

CPU

Threadswitch Event Set

Hint

Stall MLD use or HPW miss or IBQ being empty

Tlb Event Set

Tlb Event Set

Glossary

Glossary

269

Set p

EAR

271

Measurement Configuration Files p

TLB

Symbols

Index

273

Daemon processes measuring

CPU event names shortening, 94 CPU events

275

Environment variables HP Caliper, 104 Error messages

Sampled measurements performing

277

Useparensforstatementdata constant