Document Number 9S12C128DGV1/D

Revision History

Device User Guide 9S12C128DGV1/D

Table of Contents

Resets and Interrupts

System Clock Description Modes of Operation

HCS12 Core Block Description

Voltage Regulator Vreg Block Description

Appendix B Electrical Specifications

Appendix D Package Information

Appendix C Electrical Specifications

Appendix E Emulation Information

Device User Guide 9S12C128DGV1/D

List of Figures

Device User Guide 9S12C128DGV1/D

List of Tables

Device User Guide 9S12C128DGV1/D

Device User Guide 9S12C128DGV1/D

Device User Guide 9S12C128DGV1/D

Preface

List of MC9S12C and MC9S12GC Family members

MC9S12C-Family Package Option Summary

Package Device Part Number Mask Temp Flash

Part Number Mask Temp Package Speed Description Set

Speed Options 25 = 25MHz bus 16 = 16MHz bus

TBD 48LQFP

MC9S12C96PCFA16

MC9S12C96PCPB16

MC9S12C96PCFU16

MC9S12C96PVFA16

MC9S12C96PMFA25

MC9S12C96PMPB25

MC9S12C96PMFU25

MC9S12C64PCFA16

MC9S12GC-Family Part Number Coding

MC9S12GC64CFA25 TBD

MC9S12GC64CPB25 TBD

MC9S12GC64CFU25 TBD

MC9S12GC64PVFA25

Document References

Terminology

User Guide Version Document Order Number

Device User Guide 9S12C128DGV1/D

Introduction

Features

Overview

Device User Guide 9S12C128DGV1/D

Modes of Operation

Special Test ModeMotorola use only

Block Diagram

MC9S12C-Family Block Diagram

Device Register Map Overview

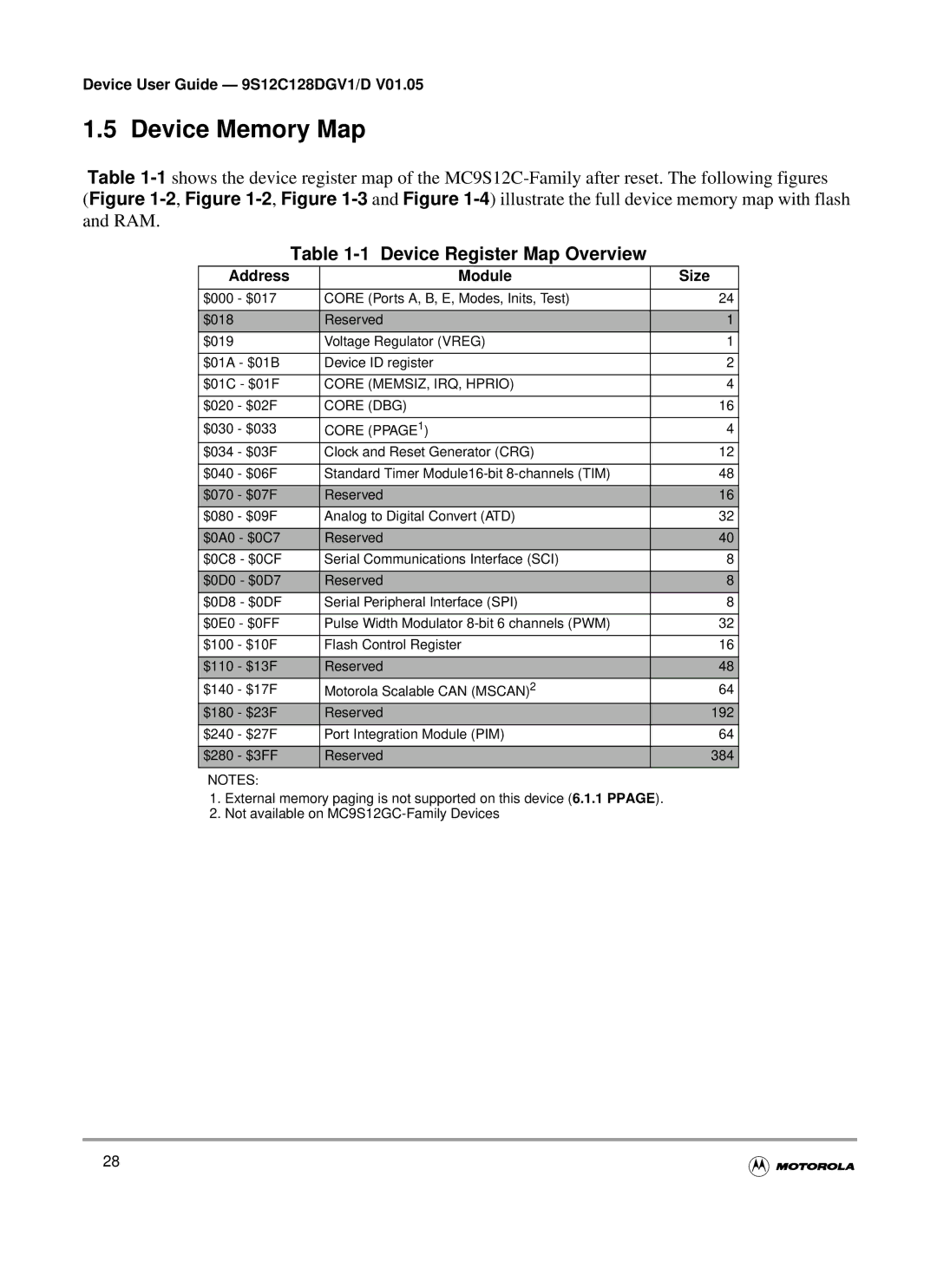

Device Memory Map

Address Module Size

MC9S12C128 and MC9S12GC128 User configurable Memory Map

MC9S12C96 User Configurable Memory Map

MC9S12C64 and MC9S12GC64 User Configurable Memory Map

MC9S12C32 and MC9S12GC32 User Configurable Memory Map

MC9S12GC16 User Configurable Memory Map

Detailed Register Map

$0010 $0014 MMC map 1 of 4 HCS12 Module Mapping Control

Ivis

$0015 $0016 INT map 1 of 2 HCS12 Interrupt

$0017 $0017 MMC map 2 of 4 HCS12 Module Mapping Control

$0018 $0018

Miscellaneous Peripherals Device User Guide

$001F $001F INT map 2 of 2 HCS12 Interrupt

$0020 $002F DBG including BKP map 1 of 1 HCS12 Debug

$0034 $003F CRG Clock and Reset Generator

$0030 $0031 MMC map 4 of 4 HCS12 Module Mapping Control

$0040 $006F TIM Timer 16 Bit 8 Channels

$0050

$0070 $007F

$00A0 $00C7

Reserved

$00C8 $00CF SCI Asynchronous Serial Interface

$00D0 $00D7

Reserved $00D8 $00DF SPI Serial Peripheral Interface

TIE

$00E0 $00FF PWM Pulse Width Modulator

$0100 $010F Flash Control Register

$0140 $017F Reserved Can Motorola Scalable can MSCAN1

$0110 $013F

Time

$0140 $017F Can Motorola Scalable can MSCAN1

$0180 $023F

Reserved $0240 $027F PIM Port Interface Module

PRIO7 PRIO6 PRIO5 PRIO4 PRIO3 PRIO2 PRIO1 PRIO0

MODRR4 MODRR3 MODRR2 MODRR1 MODRR0

Ptis

PTAD7 PTAD6 PTAD5 PTAD4 PTAD3 PTAD2 PTAD1 PTAD0

PTIAD7 PTIAD6 PTIAD5 PTIAD4 PTIAD3 PTIAD2 PTIAD1 PTIJ7

DDRAD7

DDRAD2

Part ID Assignments

$0280 $03FF Reserved space

Assigned Part ID Numbers

Memory size registers

MC9S12C32, MC9S12GC32

Signal Description

Device Pinout

PW0/IOC0/PT0 PW1/IOC1/PT1 PW2/IOC2/PT2 PW3/IOC3/PT3

PW4/IOC4/PT4

Pin Assignments in 48 Lqfp for MC9S12C-Family

Signal Properties Summary

Signal Properties

Internal Pull

Resistor Description Function Domain

Pin Initialization for 48 & 52 Pin Lqfp bond-out versions

Device User Guide 9S12C128DGV1/D Internal Pull Pin Name

Detailed Signal Descriptions

EXTAL, Xtal Oscillator Pins

Reset External Reset Pin

Test / VPP Test Pin

Bkgd / Taghi / Modc Background Debug, Tag High & Mode Pin

6 PA70 / ADDR158 / DATA158 Port a I/O Pins

7 PB70 / ADDR70 / DATA70 Port B I/O Pins

8 PE7 / Noacc / Xclks Port E I/O Pin

Colpitts Oscillator Connections PE7=1

Pierce Oscillator Connections PE7=0

9 PE6 / Modb / IPIPE1 Port E I/O Pin

10 PE5 / Moda / IPIPE0 Port E I/O Pin

11 PE4 / ECLK- Port E I/O Pin 4 / E-Clock Output

12 PE3 / Lstrb Port E I/O Pin 3 / Low-Byte Strobe Lstrb

16 PAD70 / AN70 Port AD I/O Pins

14 PE1 / IRQ Port E input Pin 1 / Maskable Interrupt Pin

17 PP7 / KWP7 Port P I/O Pin

18 PP6 / KWP6/ROMCTL Port P I/O Pin

19 PP50 / KWP50 / PW50 Port P I/O Pins

20 PJ76 / KWJ76 Port J I/O Pins

21 PM5 / SCK Port M I/O Pin

22 PM4 / Mosi Port M I/O Pin

Power Supply Pins

VDDA, Vssa Power Supply Pins for ATD and Vreg

5 VRH, VRL ATD Reference Voltage Input Pins

VDDPLL, Vsspll Power Supply Pins for PLL

MC9S12C-Family Power and Ground Connection Summary

Chip Configuration Summary

Modes of Operation

Security

Mode Selection

Clock Selection Based on PE7

Low Power Modes

Securing the Microcontroller

Operation of the Secured Microcontroller

Unsecuring the Microcontroller

Resets and Interrupts

Vectors

Resets

Reset Summary Table

Effects of Reset

HCS12 Core Block Description

Device-specific information

Device Visible with Ppage contents

BDM alternate clock

Extended Address Range Emulation Implications

Device Specific Flash page Mapping

Voltage Regulator Vreg Block Description

Recommended Printed Circuit Board Layout

Vregen

2 VDD1, VDD2, VSS1, VSS2

Recommended External Component Values

Component Purpose Type Value

Recommended PCB Layout 48 Lqfp

Recommended PCB Layout 52 Lqfp

Recommended PCB Layout 80 QFP

VSS2

Recommended PCB Layout for 48 Lqfp Pierce Oscillator

Recommended PCB Layout for 52 Lqfp Pierce Oscillator

Clock Reset Generator CRG Block Description

Recommended PCB Layout for 80QFP Pierce Oscillator

Timer TIM Block Description

Oscillator OSC Block Description

Analog to Digital Converter ATD Block Description

Serial Communications Interface SCI Block Description

Flash Block Description

RAM Block Description

Pulse Width Modulator PWM Block Description

Mscan Block Description

Device User Guide 9S12C128DGV1/D

Appendix a Electrical Characteristics

Power Supply

General

Parameter Classification

Pins

Current Injection

Absolute Maximum Ratings

Num Rating Symbol Min Max Unit

Table A-1 Absolute Maximum Ratings

Table A-3 ESD and Latch-Up Protection Characteristics

Model Description Symbol Value Unit

ESD Protection and Latch-up Immunity

Operating Conditions

Rating Symbol Min Typ Max Unit

Power Dissipation and Thermal Characteristics

Table A-4 Operating Conditions

Pint = IDD ⋅ VDD + Iddpll ⋅ Vddpll + Idda ⋅ Vdda

Table A-5 Thermal Package Characteristics1

9 I/O Characteristics

Num Rating Symbol Min Typ Max Unit

Table A-6 5V I/O Characteristics

Table A-7 3.3V I/O Characteristics

Num Rating Symbol Min Typ

Measurement Conditions

Supply Currents

Additional Remarks

Table A-8 Supply Current Characteristics for MC9S12C32

Stop Current 40 C 27 C

Appendix B Electrical Specifications

Characteristic Symbol Min Typical Max Unit

Voltage Regulator Operating Conditions

Table B-1 Voltage Regulator Electrical Parameters

Chip Power-up and LVI/LVR graphical explanation

Output Loads

Resistive Loads

LVI

Capacitive Loads

Num Characteristic Symbol Min Typical Max Unit

Table B-2 Voltage Regulator Capacitive Loads

Device User Guide 9S12C128DGV1/D

ATD Characteristics

ATD Operating Characteristics In 5V Range

ATD Operating Characteristics In 3.3V Range

Table B-3 ATD Operating Characteristics

Table B-4 ATD Operating Characteristics

Factors influencing accuracy

Source Resistance

Source capacitance

Table B-5 ATD Electrical Characteristics

Current injection

ATD accuracy 5V Range

ATD accuracy 3.3V Range

Table B-6 ATD Conversion Performance

Table B-7 ATD Conversion Performance

1LSB

Figure B-2 ATD Accuracy Definitions

NVM, Flash and Eeprom

NVM timing

Single Word Programming

Row Programming

Sector Erase

Table B-8 NVM Timing Characteristics

Mass Erase

Table B-9 NVM Reliability Characteristics

NVM Reliability

108

Reset, Oscillator and PLL

Startup

External Reset

Stop Recovery

Pseudo Stop and Wait Recovery

Oscillator

Table B-11 Oscillator Characteristics

Phase Locked Loop

XFC Component Selection

Figure B-3 Basic PLL functional diagram

XFC Pin

⋅ synr +

Jitter Information

= max ⎜ ⋅ t nom

Table B-12 PLL Characteristics

116

Table B-13 Mscan Wake-up Pulse Characteristics

Num Rating Symbol Min Typ Max

118

Appendix C Electrical Specifications

Master Mode

Table C-1 Measurement Conditions

Description Value Unit

Table C-2 SPI Master Mode Timing Characteristics

Num Characteristic Symbol Unit Min Typ Max

Mosi Port Data

LSB Master LSB OUT

Slave Mode

Input SCK

Input Miso

Slave MSB

Table C-3 SPI Slave Mode Timing Characteristics

Num Characteristic Symbol Unit Min Typ

Mosi Input Slave MSB OUT

Slave LSB OUT

External Bus Timing

General Muxed Bus Timing

Eclk PE4

PE2 Lstrb PE3 Noacc PE7 PIPO0 PIPO1, PE6,5

Table C-4 Expanded Bus Timing Characteristics 5V Range

Pweh

Table C-5 Expanded Bus Timing Characteristics 3.3V Range

126

Appendix D Package Information

Figure D-1 80-pin QFP Mechanical Dimensions case no B

80-pin QFP package

Figure D-2 52-pin Lqfp Mechanical Dimensions case no D-03

52-pin Lqfp package

48-pin Lqfp package

Section AE-AE Detail AD

Appendix E Emulation Information

1 PK20 / XADDR1614

112-pin Lqfp package

134

Device User Guide End Sheet

136