| clock cycle. Instructions can be sent simultaneously to three types of |

| independent execution units (branch units, |

| |

| out of order. PowerPC is used by Motorola, Inc. under license from |

| IBM. |

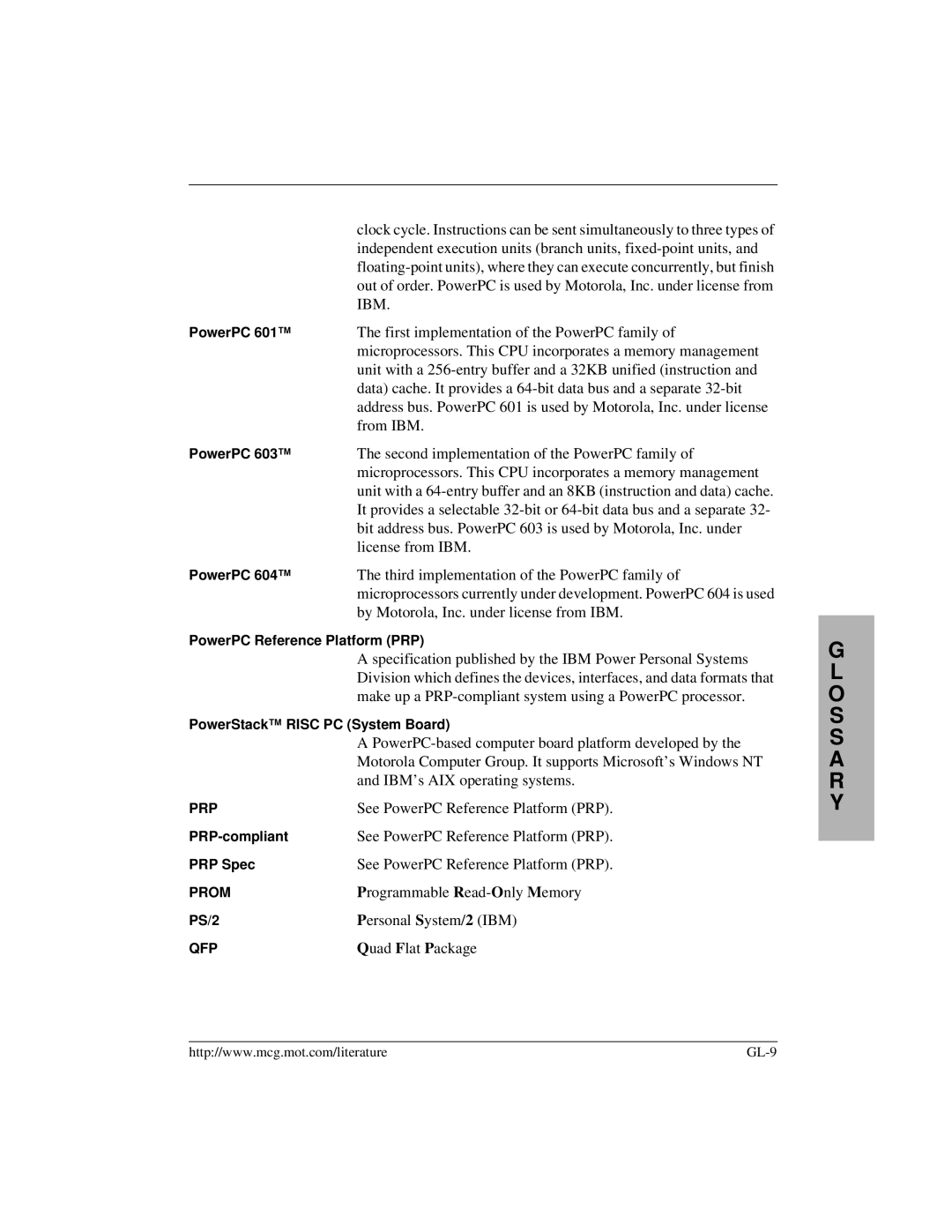

PowerPC 601™ | The first implementation of the PowerPC family of |

| microprocessors. This CPU incorporates a memory management |

| unit with a |

| data) cache. It provides a |

| address bus. PowerPC 601 is used by Motorola, Inc. under license |

| from IBM. |

PowerPC 603™ | The second implementation of the PowerPC family of |

| microprocessors. This CPU incorporates a memory management |

| unit with a |

| It provides a selectable |

| bit address bus. PowerPC 603 is used by Motorola, Inc. under |

| license from IBM. |

PowerPC 604™ | The third implementation of the PowerPC family of |

| microprocessors currently under development. PowerPC 604 is used |

| by Motorola, Inc. under license from IBM. |

PowerPC Reference Platform (PRP) | |

| A specification published by the IBM Power Personal Systems |

| Division which defines the devices, interfaces, and data formats that |

| make up a |

PowerStack™ RISC PC (System Board) | |

| A |

| Motorola Computer Group. It supports Microsoft’s Windows NT |

| and IBM’s AIX operating systems. |

PRP | See PowerPC Reference Platform (PRP). |

See PowerPC Reference Platform (PRP). | |

PRP Spec | See PowerPC Reference Platform (PRP). |

PROM | Programmable |

PS/2 | Personal System/2 (IBM) |

QFP | Quad Flat Package |

G L O S S A R Y

http://www.mcg.mot.com/literature |