TMS320C6454 Fixed-Point Digital Signal Processor

Features

Description

1 ZTZ/GTZ BGA Package Bottom View

ZTZ/GTZ 697-PIN Ball Grid Array BGA Package Bottom View

Submit Documentation Feedback

Functional Block Diagram

Functional Block Diagram

Contents

Temperature Unless Otherwise Noted

Hardware Features

Device Characteristics

Characteristics of the C6454 Processor

C6454

Fixed-Point Digital Signal Processor

CPU DSP Core Description

Product Preview

Preview

C6454 Memory Map Summary

Memory Map Summary

Memory Block Description Block Size Bytes HEX Address Range

3CFF Ffff

2FFF Ffff

Ffff

4FFF Ffff

Boot Sequence

Boot Modes Supported

2 2nd-Level Bootloaders

Pin Assignments

Pin Map

C6454 Pin Map Bottom View Quadrant B

C6454 Pin Map Bottom View Quadrant C

C6454 Pin Map Bottom View Quadrant D

Signal Groups Description

Gpio TOUTL0 TINPL0

TMS320C6454 Fixed-Point Digital Signal Processor

TINPL1 TOUTL1

SYSCLK4/GP1A

ACE2A

ACE5A ACE4A

ACE3A

ABE7 ABE6 ABE5 ABE4

CLKR1/GP0

HCNTL0/PSTOP HCNTL1/PDEVSEL HHWIL/PCLK HPI16 only

Hpia

Clks Shared

Rgmdclk

Mdio

Rgmdio

Mdclk

PCBE3

HHWIL/PCLK

Pidsel

HR/W/PCBE2 PINTA/GP14 HDS2/PCBE1

Terminal Functions

Terminal Functions

Type 1 IPD/IPU

Name

Emifa 64-BIT Control Signals Common to ALL Types of Memory

Emifa 64-BIT BUS Arbitration

IPD/IPU

Emifa 64-BIT ASYNCHRONOUS/SYNCHRONOUS Memory Control

AEA15

Name Emifa 64-BIT Address

AEA1916

AEA14

AEA6

Signal Name

Type 1 IPD/IPU 2DESCRIPTION

AEA3

Name Emifa 64-BIT Data

IPD/IPU Description Name

DDR2 Memory Controller 32-BIT Address

IPD/IPU Description Name DDR2 Memory Controller 32-BIT Data

Timer

INTER-INTEGRATED Circuit I2C

Management Data INPUT/OUTPUT Mdio for MII/RMII/GMII

Multichannel Buffered Serial Port 1 McBSP1

Multichannel Buffered Serial Port 0 McBSP0

Management Data INPUT/OUTPUT Mdio for Rgmii

Ethernet MAC Emac Rgmii

Reserved for Test

RSV14

RSV12

RSV13

RSV15

RSV19

RSV17

RSV18

RSV20

Supply Voltage Pins

Supply Voltage Monitor Pins

IPD/IPU Description

E18

AB7

AA1 AA6

AC6 AC9

AF1

AD5 AD7

AE6 AE8

CV DD

Ground Pins

GND

F20 F22 F24 G11 G13 G15 G17 G19 G21 G23

M16 M18 M24 M26 M29 N13 N15 N17 N19 N23 P12 P14 P16 P18

AB6

AA2 AA7

AC7 AC8

AF2

AD6

AE4 AE7

AH1

Device Support

Development

Development Support

Device and Development-Support Tool Nomenclature

Device Family

Temperature Range

Prefix

Device

Product Preview

Configuration IPD PIN

Device Configuration at Device Reset

C6454 Device Configuration Pins AEA190, ABA10, and Pcien

AEA15

AEA8

AEA14

AEA13

AEA6

AEA6 PIN AEA8 PIN AEA14 PIN

Peripheral Configuration at Device Reset

PCI

Lower Upper

MACSEL10 Peripheral Selection Emac

Peripheral Selection After Device Reset

Peripheral States

Static Powerdown Reset Enable Progress Disabled Enabled

Unlock the PERCFG0 register by Using the Perlock register

Device State Control Registers

Device State Control Registers

HEX Address Range Acronym Register Name

Bit Field Value Description 310

Peripheral Lock Register Description

Lockval

Lockval

Bit Field

Peripheral Configuration Register 0 Description

Description

Mode control for I2C

DDR2CTL Emifactl

Peripheral Configuration Register 1 Description

DDR2CTL

Hpistat

I2CSTAT Gpiostat TIMER1STAT TIMER0STAT Emacstat

Peripheral Status Registers Description

I2CSTAT

1715

Pcistat

Emac Configuration Register Emaccfg Description

Rmiirst

Emulator Buffer Powerdown Register Emubufpd Description

Emuctl

Sysclkout MCBSP1EN PCI66

Device Status Register Description

Emifaen DDR2EN Pcien CFGGP2 CFGGP1 CFGGP0

Pcieeai MACSEL1 MACSEL0

MACSEL10

Bit Field Value Description

Pcieeai

Lendian

Pullup/Pulldown Resistors

BOOTMODE30

Jtag ID Jtagid Register Description

Variant Part Number Manufacturer LSB

Product Preview

Configuration Examples

Timers + Emac Gmii + Mdio

Internal Buses, Bridges, and Switch Fabrics

System Interconnect

Data Switch Fabric Connections

Switched Central Resource Block Diagram

TMS320C6454

Configuration Switch Fabric

SCR Connection Matrix

C64x+ Megamodule SCR Connection

Priority Allocation

Host Emac

Sram

Memory Architecture

AET

ROM a

TMS320C6454 L1P Memory Configurations

TMS320C6454 L2 Memory Configurations

Available Memory Page Protection Schemes

Memory Protection

Bandwidth Management

AID0 Bit

Megamodule Reset Global or Local

Power-Down Control

Megamodule Resets

Reset Type Megamodule

Version

Megamodule Revision

Version Revision a

Revision

C64x+ Megamodule Register Descriptions

Megamodule Interrupt Registers

Megamodule Revision Register

Megamodule Powerdown Control Registers

Megamodule Idma Registers

Megamodule Cache Configuration Registers

MAR168 Controls Emifa CE2 Range A800 0000 A8FF Ffff

Megamodule L1/L2 Memory Protection Registers

L2MPPA5

L2MPPA3

L2MPPA4

L2MPPA6

10. CPU Megamodule Bandwidth Management Registers

11. Device Configuration Registers Chip-Level Registers

HEX Address Range Acronym Register Name Comments

Recommended Operating Conditions

Cvdd

Recommended Operating Conditions

MIN NOM MAX Unit

II DC

Parameter Test Conditions MIN TYP MAX Unit

OH = MAX

TDO DVDD33 = MIN IOL = MAX

TDO

Parameter Information

1 3.3-V Signal Transition Levels

2 3.3-V Signal Transition Rates

Tester Pin Electronics

Timing Parameters and Board Routing Analysis

Power-Supply Sequencing

Recommended Clock and Control Signal Transition Behavior

Power Supplies

Power-Supply Decoupling

Product Preview

Enhanced Direct Memory Access EDMA3 Controller

EDMA3 Device-Specific Information

C6454 EDMA3 Channel Synchronization Events1

EDMA3 Channel Synchronization Events

Edma Binary Event Name Event Description Channel

C6454 EDMA3 Channel Synchronization Events

EDMA3 Peripheral Register Descriptions

EDMA3 Channel Controller Registers

DCHMAP34

DCHMAP32

DCHMAP33

DCHMAP35

Emcr

EMR

Emrh

Emcrh

Q1E0 Event Queue 1 Entry Register

QSTAT2

QSTAT0

QSTAT1

QSTAT3

EDMA3 Parameter RAM1

EDMA3 Parameter RAM

EDMA3 Transfer Controller 0 Registers

EDMA3 Transfer Controller 1 Registers

EDMA3 Transfer Controller 2 Registers

109

EDMA3 Transfer Controller 3 Registers

111

10. C6454 DSP Interrupts

Interrupts

Interrupt Sources and Interrupt Controller

Event Number Interrupt Event Interrupt Source

TINTLO1

TINTLO0

TINTHI0

TINTHI1

Idmacmpa

L2DMPA

Idmabuserr

11. Timing Requirements for External Interrupts1 see Figure

External Interrupts Electrical Data/Timing

NMI

12. Reset Types

Reset Controller

Power-on Reset POR Pin

Type Initiator

Warm Reset Reset Pin

System Reset

CPU Reset

Reset Controller Register

Reset Priority

Reset Type Status Register Description

720 1000

Reset Electrical Data/Timing

14. Timing Requirements for Reset1 2 3see -8and Figure

Parameter

Power-Up Timing

TMS320C6454

Resetstat

CLKIN1 CLKIN2 POR

PLL1 and PLL1 Controller

1 PLL1 Controller Device-Specific Information

Internal Clocks and Maximum Operating Frequencies

16. PLL1 Clock Frequency Ranges

1.3 PLL1 Stabilization, Lock, and Reset Times

Clock Signal MIN MAX Unit

1.2 PLL1 Controller Operating Modes

2 PLL1 Controller Memory Map

17. PLL1 Stabilization, Lock, and Reset Times

18. PLL1 Controller Registers Including Reset Controller

MIN TYP

Pllrst

3 PLL1 Controller Register Descriptions

3.1 PLL1 Control Register

Pllpwrdn

PLL Multiplier Control Register

20. PLL Multiplier Control Register Pllm Field Descriptions

Preden

PLL Pre-Divider Control Register

Ratio

PLL Controller Divider 4 Register

D4EN

PLL Controller Divider 5 Register

D5EN

PLL Controller Command Register

Goset

PLL Controller Status Register

Gostat

PLL Controller Clock Align Control Register

SYS5 SYS4

Plldiv Ratio Change Status Register

SYS5

Sysclk Status Register

SYS5ON SYS4ON SYS3ON SYS2ON

PLL Modes Unit

29. Timing Requirements for CLKIN1 Devices1 2 3 see Figure

720 850 1000

X1 Bypass X20, x25, x30

PLL2 and PLL2 Controller

1.2 PLL2 Controller Operating Modes

1 PLL2 Controller Device-Specific Information

31. PLL2 Clock Frequency Ranges

Pllref Pllen =

32. PLL2 Controller Registers

2 PLL2 Controller Memory Map

3 PLL2 Controller Register Descriptions

HEX Address Range Acronym Description

PLL Controller Divider 1 Register

D1EN

PLL Controller Command Register

ALN1

SYS1

SYS1ON

4 PLL2 Controller Input Clock Electrical Data/Timing

39. Timing Requirements for CLKIN21 2 3 see Figure

DDR2 Memory Controller

1 DDR2 Memory Controller Device-Specific Information

3 DDR2 Memory Controller Electrical Data/Timing

2 DDR2 Memory Controller Peripheral Register Descriptions

40. DDR2 Memory Controller Registers

External Memory Interface a Emifa

Emifa Device-Specific Information

Emifa Peripheral Register Descriptions

41. Emifa Registers

42. Timing Requirements for Aeclkin for EMIFA1 2 see Figure

Emifa Electrical Data/Timing

Aeclkin

Aeclkin AECLKOUT1

720

720 850 1000UNIT

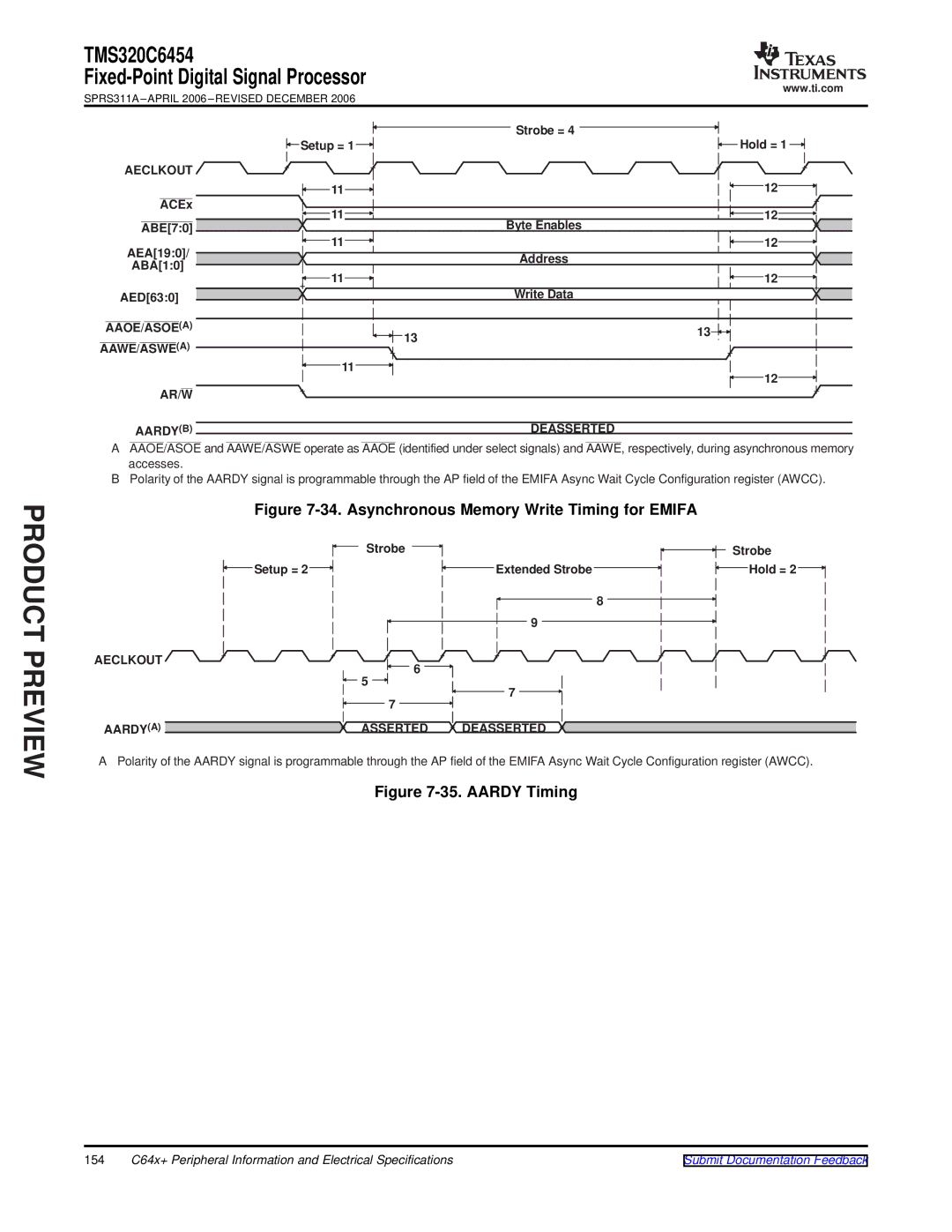

ABA10 AED630 Read Data

Setup = Hold =

ACEx ABE70

AAOE/ASOE a AAWE/ASWE a AR/W Aardy B Deasserted

ABA10 AED630

Strobe Setup = Extended Strobe

Aeclkout Aardya Asserted Deasserted

155

EA1 EA2 EA3 EA4

BE1 BE2 BE3 BE4

AEA190/ABA10

ASADS/ASREB AAOE/ASOEB AAWE/ASWEB

Write Latency =

DSP Owns Bus

HOLD/HOLDA Timing

HHOLDAL-HOLDL Hold time, Hold low after Holda low

Hold Holda

Delay time, Aeclkout high to Abusreq valid AECLKOUTx

Busreq Timing

11 I2C Peripheral

11.1 I2C Device-Specific Information

I2CCLKH I2CSAR

I2COAR

SCL

I2CXSR

11.2 I2C Peripheral Register Descriptions

51. I2C Registers

Standard Mode Fast Mode MIN MAX

11.3 I2C Electrical Data/Timing

Stop Start Repeated

SDA SCL

Unit MAX

Stop Start

Start Stop

HPI Peripheral Register Descriptions

Host-Port Interface HPI Peripheral

HPI Device-Specific Information

54. HPI Control Registers

HPI Electrical Data/Timing

See -56through Figure

HR/W Hhwil Hstrobea

HCS Has

HCNTL10

HD150

HR/W Hhwil Hstrobe a

Hrdyb

46. HPI16 Write Timing has Not Used, Tied High

47. HPI16 Write Timing has Used

Has input HCNTL10 input HR/W input

HCS input HD310 output Hrdyb output

49. HPI32 Read Timing has Used

50. HPI32 Write Timing has Not Used, Tied High

Input HCS input

51. HPI32 Write Timing has Used

Input HCS input HD310 input

Multichannel Buffered Serial Port McBSP

McBSP Device-Specific Information

58. McBSP 1 Registers

McBSP Electrical Data/Timing

Product

181

Clkx

Clks Clkr

Clks

Slave MIN MAX

Master Slave MIN MAX

Clkx FSX

Master Slave MIN

Setup time, DR valid before Clkx high 18P

Hold time, DR valid after Clkx high + 36P

186

Ethernet MAC Emac

Ethernet Bus

Emac Device-Specific Information

Interface Modes

Ball Number Device PIN Name

70. EMAC/MDIO Multiplexed Pins MII, RMII, and Gmii Modes

Rmii

Interface Mode Clocking

Emac Peripheral Register Descriptions

71. Ethernet MAC Emac Control Registers

RX5FREEBUFFER

Macconfig

Softreset

RX6FREEBUFFER

72. Emac Statistics Registers

HEX Address Range Acronym

74. Emac Descriptor Memory

73. Emac Control Module Registers

02C8 2000 02C8 3FFF Emac Descriptor Memory

Emac Electrical Data/Timing

Mtclk

Mrclk Input MRXD7−MRXD4GMII only

Output 720 1000UNIT 1000 Mbps

1000 Mbps 100/10 Mbps

MRXD3−MRXD0

NO.PARAMETER

MTXD3−MTXD0

MTXD7−MTXD0

Emac Rmii Electrical Data/Timing

Rmrefclk

MRXD1-MRXD0 Mcrsdv

Rmrefclk Input

Mrxer Inputs 720 1000

Emac Rgmii Electrical Data/Timing

Output

201

70. Emac Transmit Interface Timing Rgmii OperationAB

Mdio Device-Specific Information

Management Data Input/Output Mdio

Mdio Peripheral Register Descriptions 89. Mdio Registers

Mdio input

Delay time, Mdclk low to Mdio data output valid 100

Mdio output

Timers Peripheral Register Descriptions

Timers

Timers Device-Specific Information

92. Timer 0 Registers

94. Timing Requirements for Timer Inputs1 see Figure

Timers Electrical Data/Timing

TINPLx TOUTLx

Peripheral Component Interconnect PCI

96. Default Values for PCI Configuration Registers

Register Default Value

PCI Device-Specific Information

97. PCI Configuration Registers

PCI Peripheral Register Descriptions

98. PCI Back End Configuration Registers

99. DSP-toPCI Address Translation Registers

101. PCI External Memory Space

100. PCI Hook Configuration Registers

HEX Address Offset Acronym Register Name

49FF Ffff

47FF Ffff

48FF Ffff

4A7F Ffff

PCI Electrical Data/Timing

Gpio Peripheral Register Descriptions

General-Purpose Input/Output Gpio

Gpio Device-Specific Information

102. Gpio Registers

103. Timing Requirements for Gpio Inputs1 2 see Figure

Gpio Electrical Data/Timing

GPIx GPOx

Ieee 1149.1 Jtag Compatibility Statement

Ieee 1149.1 Jtag

Jtag Device-Specific Information

105. Timing Requirements for Jtag Test Port see Figure

Packaging Information

Thermal Resistance Characteristics S-PBGA Package ZTZ/GTZ

Thermal Data

AIR Flow

C6454 Revision History

Revision History

See ADDITIONS/MODIFICATIONS/DELETIONS

Changed -4title to EDMA3 Channel Controller Registers

Product Preview

Revision History 221

MSL Peak Temp

Orderable Device Status Package

Eco Plan

Qty

Page

Page

Important Notice

ASSERTED

ASSERTED  DEASSERTED

DEASSERTED