PRODUCT PREVIEW

TMS320C6454

www.ti.com

SPRS311A

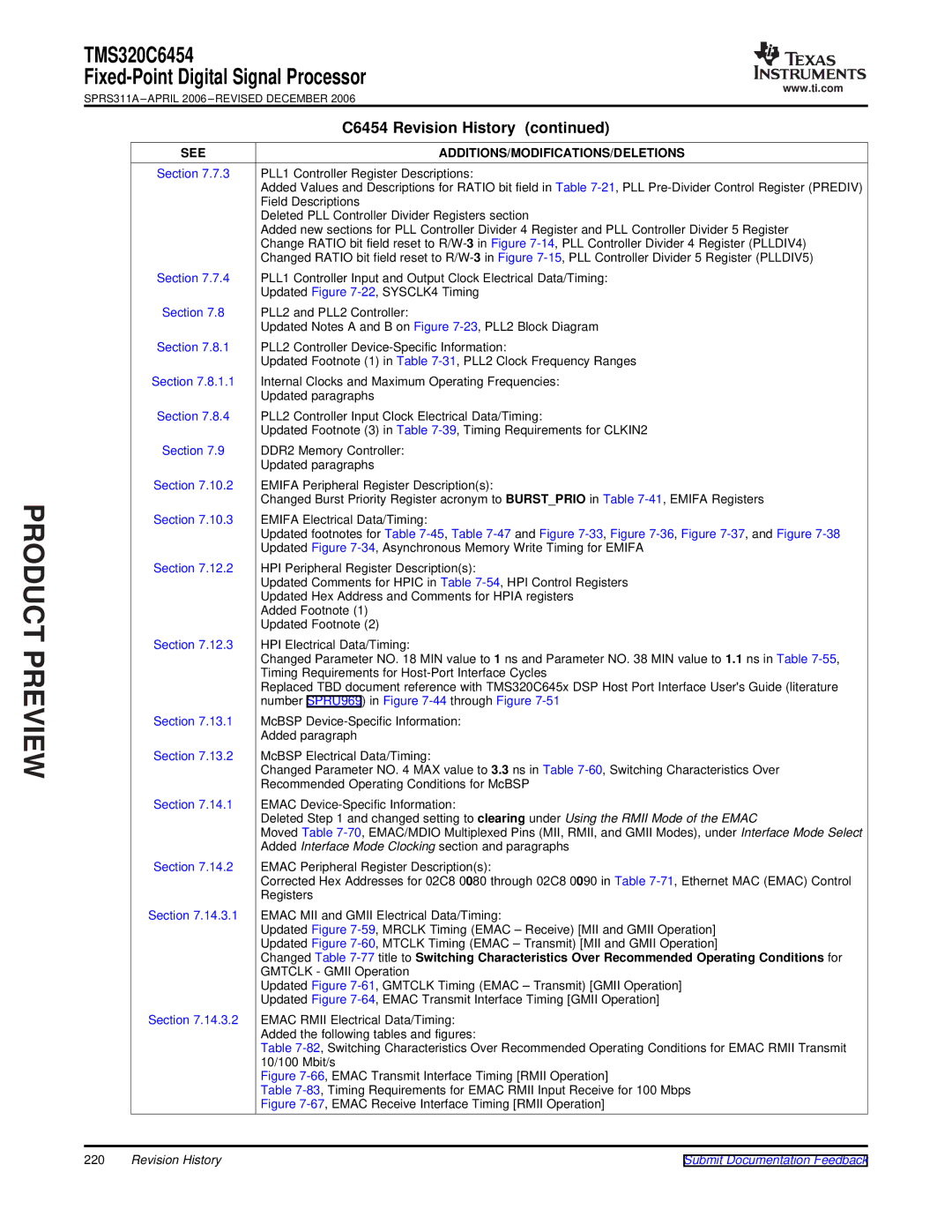

C6454 Revision History (continued)

SEE | ADDITIONS/MODIFICATIONS/DELETIONS |

Section 7.7.3 PLL1 Controller Register Descriptions:

Added Values and Descriptions for RATIO bit field in Table

Deleted PLL Controller Divider Registers section

Added new sections for PLL Controller Divider 4 Register and PLL Controller Divider 5 Register Change RATIO bit field reset to

Section 7.7.4 PLL1 Controller Input and Output Clock Electrical Data/Timing:

Updated Figure

Section 7.8 PLL2 and PLL2 Controller:

Updated Notes A and B on Figure

Section 7.8.1 PLL2 Controller

Updated Footnote (1) in Table

Section 7.8.1.1 Internal Clocks and Maximum Operating Frequencies:

Updated paragraphs

Section 7.8.4 PLL2 Controller Input Clock Electrical Data/Timing:

Updated Footnote (3) in Table

Section 7.9 DDR2 Memory Controller:

Updated paragraphs

Section 7.10.2 EMIFA Peripheral Register Description(s):

Changed Burst Priority Register acronym to BURST_PRIO in Table

Section 7.10.3 EMIFA Electrical Data/Timing:

Updated footnotes for Table

Section 7.12.2 HPI Peripheral Register Description(s):

Updated Comments for HPIC in Table

Updated Hex Address and Comments for HPIA registers

Added Footnote (1)

Updated Footnote (2)

Section 7.12.3 HPI Electrical Data/Timing:

Changed Parameter NO. 18 MIN value to 1 ns and Parameter NO. 38 MIN value to 1.1 ns in Table

Replaced TBD document reference with TMS320C645x DSP Host Port Interface User'sGuide (literature number SPRU969) in Figure

Section 7.13.1 McBSP

Added paragraph

Section 7.13.2 McBSP Electrical Data/Timing:

Changed Parameter NO. 4 MAX value to 3.3 ns in Table

Section 7.14.1 EMAC

Deleted Step 1 and changed setting to clearing under Using the RMII Mode of the EMAC

Moved Table

Section 7.14.2 EMAC Peripheral Register Description(s):

Corrected Hex Addresses for 02C8 0080 through 02C8 0090 in Table

Section 7.14.3.1 EMAC MII and GMII Electrical Data/Timing:

Updated Figure

Updated Figure

Changed Table

GMTCLK - GMII Operation

Updated Figure

Updated Figure

Section 7.14.3.2 EMAC RMII Electrical Data/Timing:

Added the following tables and figures:

Table

Figure 7-66, EMAC Transmit Interface Timing [RMII Operation]

Table 7-83, Timing Requirements for EMAC RMII Input Receive for 100 Mbps Figure 7-67, EMAC Receive Interface Timing [RMII Operation]

220 | Revision History | Submit Documentation Feedback |