PWM Output Function |

|

Pulse Enable Flag (Device) | M336 |

Frequency Setting Register | MW22, MW23 |

ON duty setting register | MW24, MW25 |

pulse width error flag | M189 |

On duty setting error flag | M190 |

Frequency Setting Error Flag (Device) | M191 |

|

|

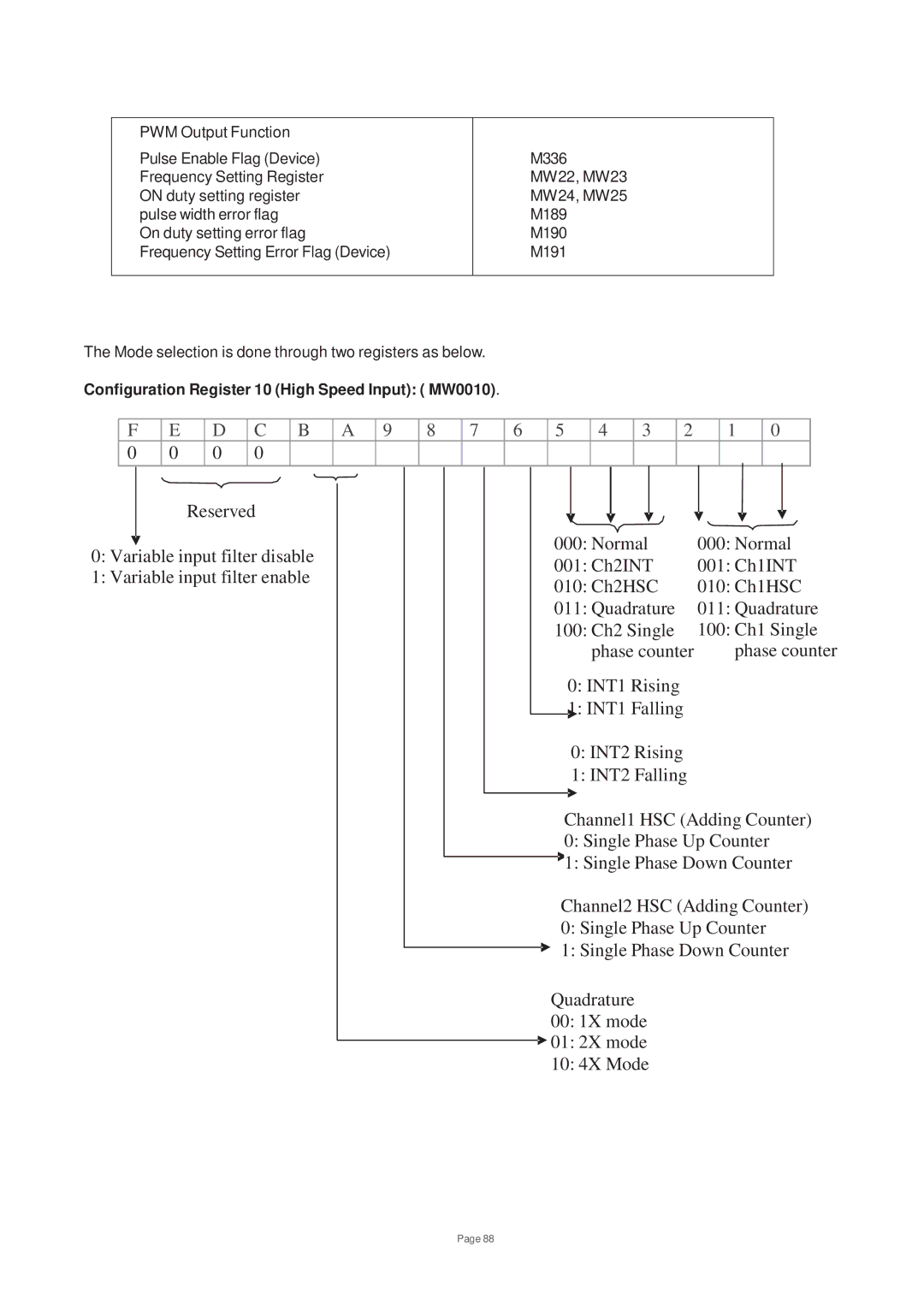

The Mode selection is done through two registers as below.

Configuration Register 10 (High Speed Input): ( MW0010).

F 0

E 0

D 0

C B A 9 8 7 6 5 4 3 2 1 0 0

Reserved |

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

0: Variable input filter disable |

|

|

|

| 000: Normal | 000: Normal | |

|

|

|

| 001: Ch2INT | 001: Ch1INT | ||

1: Variable input filter enable |

|

|

|

| |||

|

|

|

| 010: Ch2HSC | 010: Ch1HSC | ||

|

|

|

|

| |||

|

|

|

|

| 011: Quadrature | 011: Quadrature | |

|

|

|

|

| 100: Ch2 Single | 100: Ch1 Single | |

|

|

|

|

|

| phase counter | phase counter |

|

|

|

|

|

| 0: INT1 Rising |

|

|

|

|

|

|

| 1: INT1 Falling |

|

|

|

|

|

|

| ||

|

|

|

|

|

| 0: INT2 Rising |

|

|

|

|

|

|

| 1: INT2 Falling |

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

| |

|

|

|

|

|

| Channel1 HSC (Adding Counter) | |

|

|

|

|

|

| 0: Single Phase Up Counter | |

|

|

|

|

|

| 1: Single Phase Down Counter | |

|

|

|

|

| |||

|

|

|

|

|

|

| |

|

|

|

|

| Channel2 HSC (Adding Counter) | ||

|

|

|

|

| 0: Single Phase Up Counter | ||

|

|

|

|

| 1: Single Phase Down Counter | ||

|

|

|

|

| |||

|

|

|

|

| Quadrature |

| |

|

|

|

|

| 00: 1X mode |

| |

|

|

|

|

| 01: 2X mode |

| |

|

|

|

|

|

| ||

|

|

|

|

| 10: 4X Mode |

| |

Page 88