Detailed Description

12. USB-to-UART Bridge

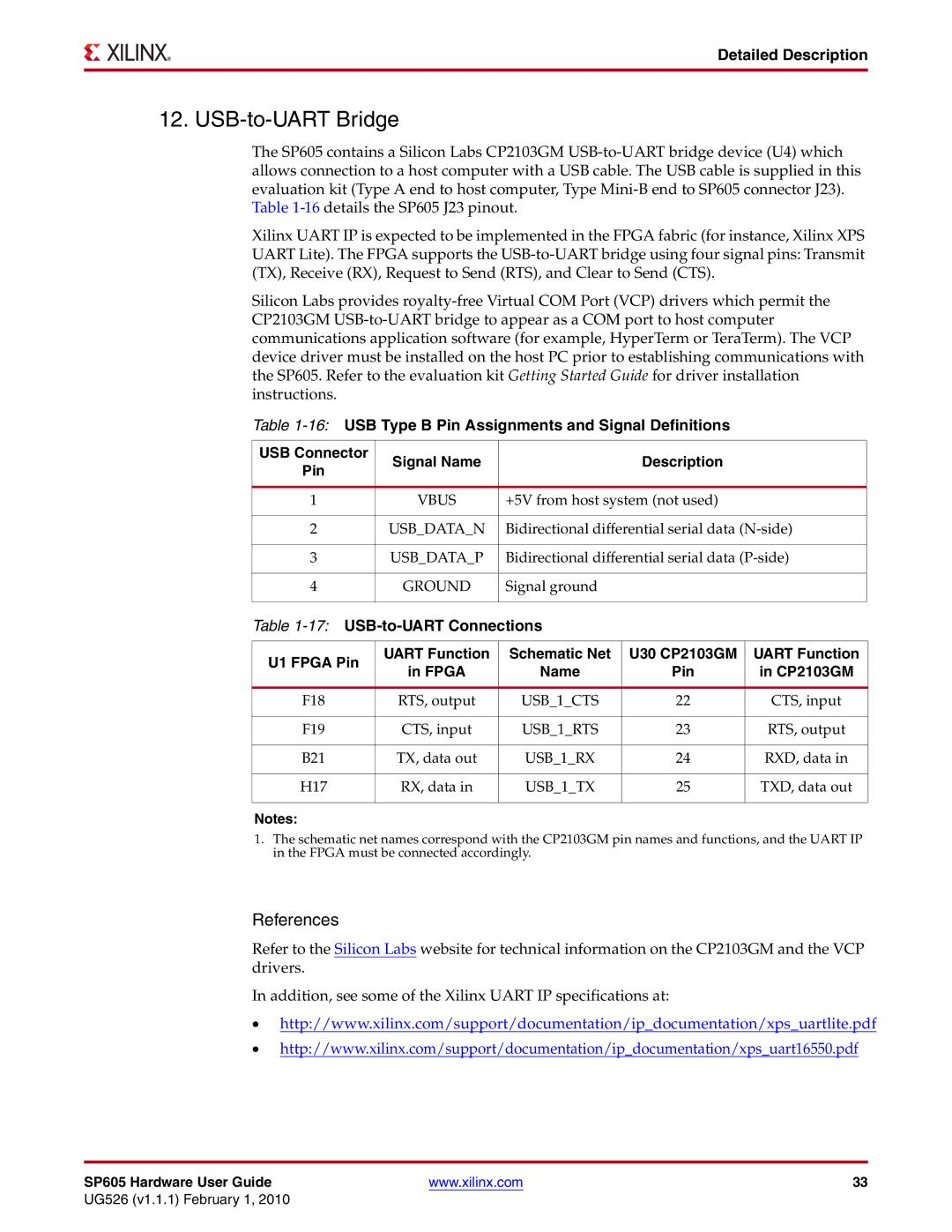

The SP605 contains a Silicon Labs CP2103GM

Xilinx UART IP is expected to be implemented in the FPGA fabric (for instance, Xilinx XPS UART Lite). The FPGA supports the

Silicon Labs provides

Table

USB Connector | Signal Name |

| Description |

| |

Pin |

|

| |||

|

|

|

| ||

|

|

|

|

| |

1 | VBUS | +5V from host system (not used) |

| ||

|

|

|

|

| |

2 | USB_DATA_N | Bidirectional differential serial data | |||

|

|

|

|

| |

3 | USB_DATA_P | Bidirectional differential serial data | |||

|

|

|

|

| |

4 | GROUND | Signal ground |

|

| |

|

|

|

|

| |

Table |

|

| |||

|

|

|

|

| |

U1 FPGA Pin | UART Function | Schematic Net | U30 CP2103GM | UART Function | |

in FPGA | Name | Pin | in CP2103GM | ||

| |||||

|

|

|

|

| |

F18 | RTS, output | USB_1_CTS | 22 | CTS, input | |

|

|

|

|

| |

F19 | CTS, input | USB_1_RTS | 23 | RTS, output | |

|

|

|

|

| |

B21 | TX, data out | USB_1_RX | 24 | RXD, data in | |

|

|

|

|

| |

H17 | RX, data in | USB_1_TX | 25 | TXD, data out | |

|

|

|

|

| |

Notes:

1.The schematic net names correspond with the CP2103GM pin names and functions, and the UART IP in the FPGA must be connected accordingly.

References

Refer to the Silicon Labs website for technical information on the CP2103GM and the VCP drivers.

In addition, see some of the Xilinx UART IP specifications at:

•http://www.xilinx.com/support/documentation/ip_documentation/xps_uartlite.pdf

•http://www.xilinx.com/support/documentation/ip_documentation/xps_uart16550.pdf

SP605 Hardware User Guide | www.xilinx.com | 33 |

UG526 (v1.1.1) February 1, 2010