Detailed Description

User DIP Switch

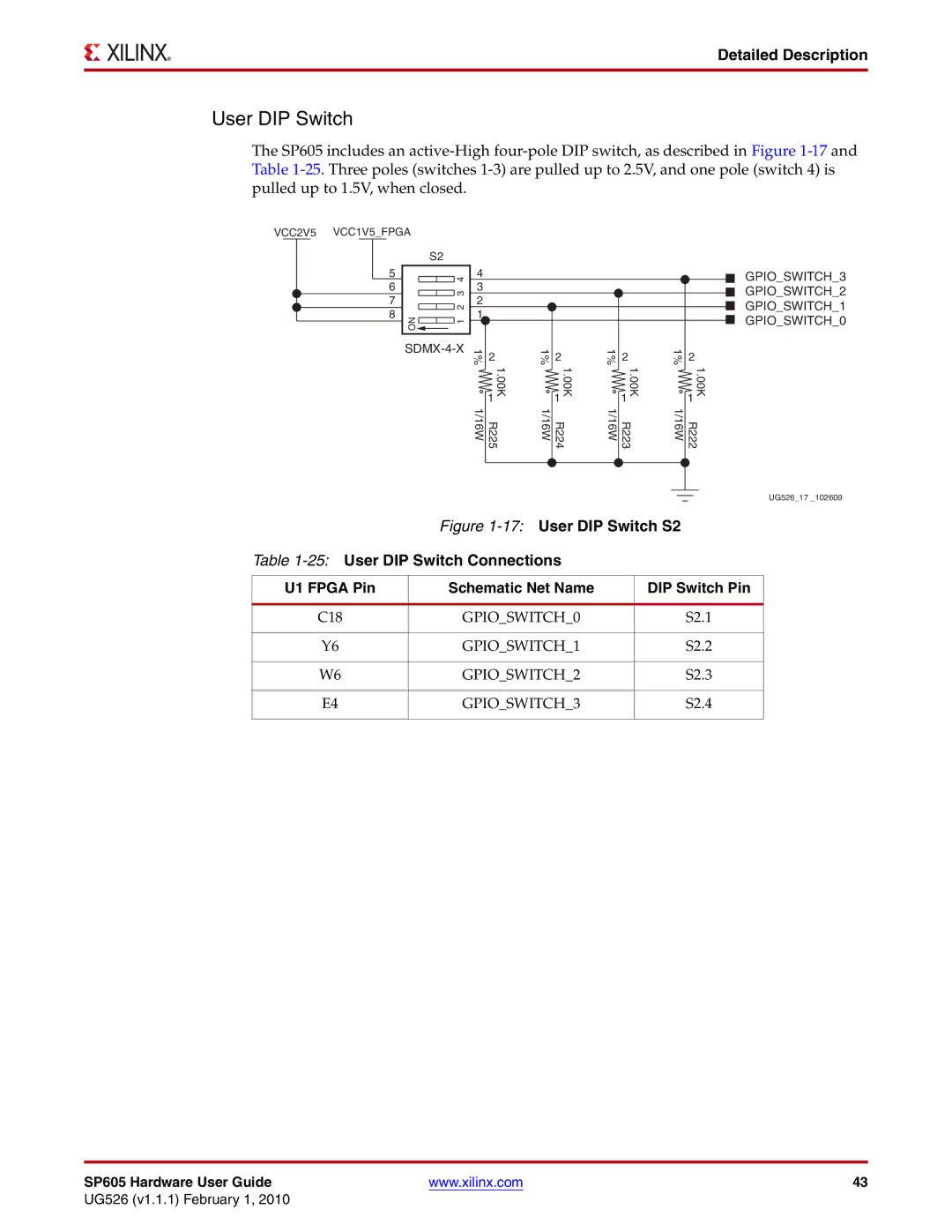

The SP605 includes an

VCC2V5 VCC1V5_FPGA

|

|

| 5 |

|

|

| S2 | |||||

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

| 4 | ||

6 |

|

|

|

|

|

|

|

| 3 | |||

7 |

|

|

|

|

|

|

|

| 2 | |||

8 | ON |

|

|

|

|

|

|

| 1 | |||

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

4

3

2

1

1% | 2 |

|

|

| |

| 1 | 1.00K |

|

| |

1/16W | R225 | |

1% 1/16W

2 |

|

1 | 1.00K |

| |

R224 | |

1% 1/16W

2 |

|

1 | 1.00K |

| |

R223 | |

1% 1/16W

2 |

|

1 | 1.00K |

| |

R222 | |

GPIO_SWITCH_3 GPIO_SWITCH_2 GPIO_SWITCH_1 GPIO_SWITCH_0

UG526_17 _102609

Figure 1-17: User DIP Switch S2

Table 1-25: User DIP Switch Connections

U1 FPGA Pin | Schematic Net Name | DIP Switch Pin |

|

|

|

C18 | GPIO_SWITCH_0 | S2.1 |

|

|

|

Y6 | GPIO_SWITCH_1 | S2.2 |

|

|

|

W6 | GPIO_SWITCH_2 | S2.3 |

|

|

|

E4 | GPIO_SWITCH_3 | S2.4 |

|

|

|

SP605 Hardware User Guide | www.xilinx.com | 43 |

UG526 (v1.1.1) February 1, 2010