Detailed Description

I/O Voltage Rails

There are four available banks on the

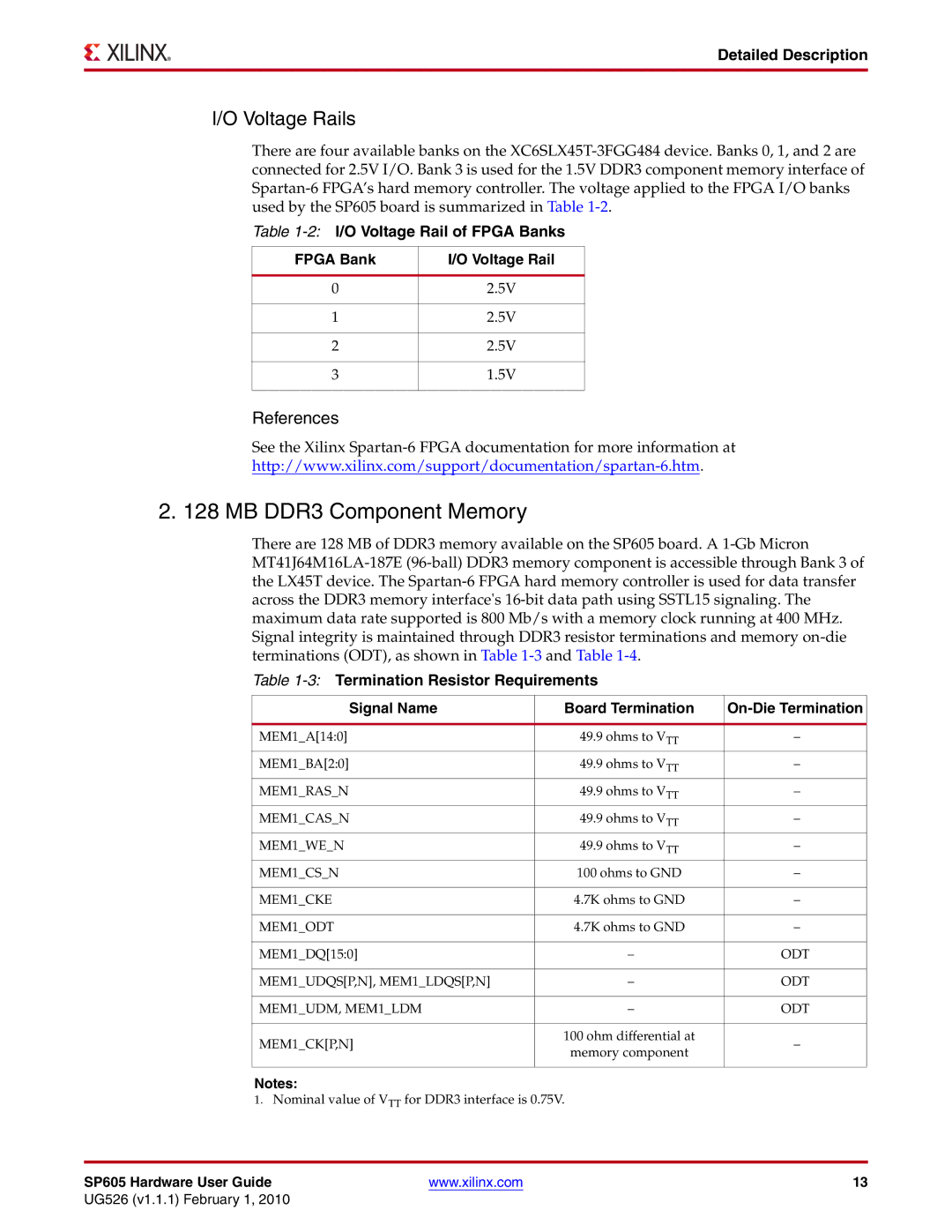

Table 1-2: I/O Voltage Rail of FPGA Banks

FPGA Bank | I/O Voltage Rail |

|

|

0 | 2.5V |

|

|

1 | 2.5V |

|

|

2 | 2.5V |

|

|

3 | 1.5V |

|

|

References

See the Xilinx

2. 128 MB DDR3 Component Memory

There are 128 MB of DDR3 memory available on the SP605 board. A

Table

Signal Name | Board Termination |

| |

|

|

| |

MEM1_A[14:0] | 49.9 ohms to VTT | – | |

MEM1_BA[2:0] | 49.9 ohms to VTT | – | |

|

|

| |

MEM1_RAS_N | 49.9 ohms to VTT | – | |

|

|

| |

MEM1_CAS_N | 49.9 ohms to VTT | – | |

|

|

| |

MEM1_WE_N | 49.9 ohms to VTT | – | |

|

|

| |

MEM1_CS_N | 100 ohms to GND | – | |

|

|

| |

MEM1_CKE | 4.7K ohms to GND | – | |

|

|

| |

MEM1_ODT | 4.7K ohms to GND | – | |

|

|

| |

MEM1_DQ[15:0] | – | ODT | |

|

|

| |

MEM1_UDQS[P,N], MEM1_LDQS[P,N] | – | ODT | |

|

|

| |

MEM1_UDM, MEM1_LDM | – | ODT | |

|

|

| |

MEM1_CK[P,N] | 100 ohm differential at | – | |

memory component | |||

|

| ||

|

|

|

Notes:

1.Nominal value of VTT for DDR3 interface is 0.75V.

SP605 Hardware User Guide | www.xilinx.com | 13 |

UG526 (v1.1.1) February 1, 2010