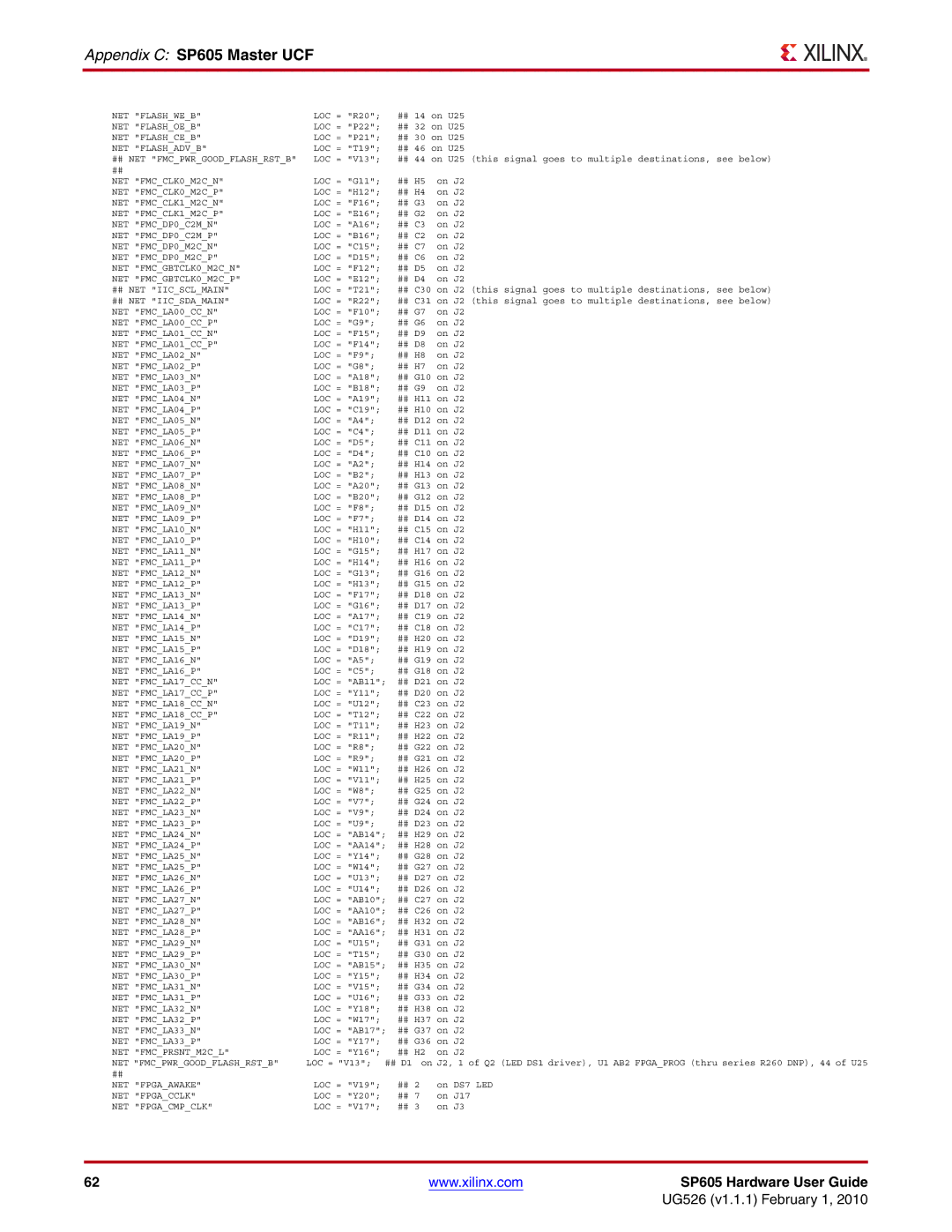

Appendix C: SP605 Master UCF

NET "FLASH_WE_B" | LOC = "R20"; | ## 14 on U25 | |

NET "FLASH_OE_B" | LOC = "P22"; | ## 32 on U25 | |

NET "FLASH_CE_B" | LOC = "P21"; | ## 30 on U25 | |

NET "FLASH_ADV_B" | LOC = "T19"; | ## 46 on U25 | |

## NET "FMC_PWR_GOOD_FLASH_RST_B" | LOC = "V13"; | ## 44 on U25 (this signal goes to multiple destinations, see below) | |

## |

|

|

|

NET "FMC_CLK0_M2C_N" | LOC = "G11"; | ## H5 | on J2 |

NET "FMC_CLK0_M2C_P" | LOC = "H12"; | ## H4 | on J2 |

NET "FMC_CLK1_M2C_N" | LOC = "F16"; | ## G3 | on J2 |

NET "FMC_CLK1_M2C_P" | LOC = "E16"; | ## G2 | on J2 |

NET "FMC_DP0_C2M_N" | LOC = "A16"; | ## C3 | on J2 |

NET "FMC_DP0_C2M_P" | LOC = "B16"; | ## C2 | on J2 |

NET "FMC_DP0_M2C_N" | LOC = "C15"; | ## C7 | on J2 |

NET "FMC_DP0_M2C_P" | LOC = "D15"; | ## C6 | on J2 |

NET "FMC_GBTCLK0_M2C_N" | LOC = "F12"; | ## D5 | on J2 |

NET "FMC_GBTCLK0_M2C_P" | LOC = "E12"; | ## D4 | on J2 |

## NET "IIC_SCL_MAIN" | LOC = "T21"; | ## C30 on J2 (this signal goes to multiple destinations, see below) | |

## NET "IIC_SDA_MAIN" | LOC = "R22"; | ## C31 | on J2 (this signal goes to multiple destinations, see below) |

NET "FMC_LA00_CC_N" | LOC = "F10"; | ## G7 | on J2 |

NET "FMC_LA00_CC_P" | LOC = "G9"; | ## G6 | on J2 |

NET "FMC_LA01_CC_N" | LOC = "F15"; | ## D9 | on J2 |

NET "FMC_LA01_CC_P" | LOC = "F14"; | ## D8 | on J2 |

NET "FMC_LA02_N" | LOC = "F9"; | ## H8 | on J2 |

NET "FMC_LA02_P" | LOC = "G8"; | ## H7 | on J2 |

NET "FMC_LA03_N" | LOC = "A18"; | ## G10 | on J2 |

NET "FMC_LA03_P" | LOC = "B18"; | ## G9 | on J2 |

NET "FMC_LA04_N" | LOC = "A19"; | ## H11 on J2 | |

NET "FMC_LA04_P" | LOC = "C19"; | ## H10 on J2 | |

NET "FMC_LA05_N" | LOC = "A4"; | ## D12 on J2 | |

NET "FMC_LA05_P" | LOC = "C4"; | ## D11 on J2 | |

NET "FMC_LA06_N" | LOC = "D5"; | ## C11 on J2 | |

NET "FMC_LA06_P" | LOC = "D4"; | ## C10 on J2 | |

NET "FMC_LA07_N" | LOC = "A2"; | ## H14 on J2 | |

NET "FMC_LA07_P" | LOC = "B2"; | ## H13 on J2 | |

NET "FMC_LA08_N" | LOC = "A20"; | ## G13 on J2 | |

NET "FMC_LA08_P" | LOC = "B20"; | ## G12 on J2 | |

NET "FMC_LA09_N" | LOC = "F8"; | ## D15 on J2 | |

NET "FMC_LA09_P" | LOC = "F7"; | ## D14 on J2 | |

NET "FMC_LA10_N" | LOC = "H11"; | ## C15 on J2 | |

NET "FMC_LA10_P" | LOC = "H10"; | ## C14 on J2 | |

NET "FMC_LA11_N" | LOC = "G15"; | ## H17 on J2 | |

NET "FMC_LA11_P" | LOC = "H14"; | ## H16 on J2 | |

NET "FMC_LA12_N" | LOC = "G13"; | ## G16 on J2 | |

NET "FMC_LA12_P" | LOC = "H13"; | ## G15 on J2 | |

NET "FMC_LA13_N" | LOC = "F17"; | ## D18 on J2 | |

NET "FMC_LA13_P" | LOC = "G16"; | ## D17 on J2 | |

NET "FMC_LA14_N" | LOC = "A17"; | ## C19 on J2 | |

NET "FMC_LA14_P" | LOC = "C17"; | ## C18 on J2 | |

NET "FMC_LA15_N" | LOC = "D19"; | ## H20 on J2 | |

NET "FMC_LA15_P" | LOC = "D18"; | ## H19 on J2 | |

NET "FMC_LA16_N" | LOC = "A5"; | ## G19 on J2 | |

NET "FMC_LA16_P" | LOC = "C5"; | ## G18 on J2 | |

NET "FMC_LA17_CC_N" | LOC = "AB11"; | ## D21 on J2 | |

NET "FMC_LA17_CC_P" | LOC = "Y11"; | ## D20 on J2 | |

NET "FMC_LA18_CC_N" | LOC = "U12"; | ## C23 on J2 | |

NET "FMC_LA18_CC_P" | LOC = "T12"; | ## C22 on J2 | |

NET "FMC_LA19_N" | LOC = "T11"; | ## H23 on J2 | |

NET "FMC_LA19_P" | LOC = "R11"; | ## H22 on J2 | |

NET "FMC_LA20_N" | LOC = "R8"; | ## G22 on J2 | |

NET "FMC_LA20_P" | LOC = "R9"; | ## G21 on J2 | |

NET "FMC_LA21_N" | LOC = "W11"; | ## H26 on J2 | |

NET "FMC_LA21_P" | LOC = "V11"; | ## H25 on J2 | |

NET "FMC_LA22_N" | LOC = "W8"; | ## G25 on J2 | |

NET "FMC_LA22_P" | LOC = "V7"; | ## G24 on J2 | |

NET "FMC_LA23_N" | LOC = "V9"; | ## D24 on J2 | |

NET "FMC_LA23_P" | LOC = "U9"; | ## D23 on J2 | |

NET "FMC_LA24_N" | LOC = "AB14"; | ## H29 on J2 | |

NET "FMC_LA24_P" | LOC = "AA14"; | ## H28 on J2 | |

NET "FMC_LA25_N" | LOC = "Y14"; | ## G28 on J2 | |

NET "FMC_LA25_P" | LOC = "W14"; | ## G27 on J2 | |

NET "FMC_LA26_N" | LOC = "U13"; | ## D27 on J2 | |

NET "FMC_LA26_P" | LOC = "U14"; | ## D26 on J2 | |

NET "FMC_LA27_N" | LOC = "AB10"; | ## C27 on J2 | |

NET "FMC_LA27_P" | LOC = "AA10"; | ## C26 on J2 | |

NET "FMC_LA28_N" | LOC = "AB16"; | ## H32 on J2 | |

NET "FMC_LA28_P" | LOC = "AA16"; | ## H31 on J2 | |

NET "FMC_LA29_N" | LOC = "U15"; | ## G31 on J2 | |

NET "FMC_LA29_P" | LOC = "T15"; | ## G30 on J2 | |

NET "FMC_LA30_N" | LOC = "AB15"; | ## H35 on J2 | |

NET "FMC_LA30_P" | LOC = "Y15"; | ## H34 on J2 | |

NET "FMC_LA31_N" | LOC = "V15"; | ## G34 on J2 | |

NET "FMC_LA31_P" | LOC = "U16"; | ## G33 on J2 | |

NET "FMC_LA32_N" | LOC = "Y18"; | ## H38 on J2 | |

NET "FMC_LA32_P" | LOC = "W17"; | ## H37 on J2 | |

NET "FMC_LA33_N" | LOC = "AB17"; | ## G37 on J2 | |

NET "FMC_LA33_P" | LOC = "Y17"; | ## G36 | on J2 |

NET "FMC_PRSNT_M2C_L" | LOC = "Y16"; | ## H2 | on J2 |

NET "FMC_PWR_GOOD_FLASH_RST_B" | LOC = "V13"; ## D1 on J2, 1 of Q2 (LED DS1 driver), U1 AB2 FPGA_PROG (thru series R260 DNP), 44 of U25 | ||

## |

|

|

|

NET "FPGA_AWAKE" | LOC = "V19"; | ## 2 | on DS7 LED |

NET "FPGA_CCLK" | LOC = "Y20"; | ## 7 | on J17 |

NET "FPGA_CMP_CLK" | LOC = "V17"; | ## 3 | on J3 |

62 | www.xilinx.com | SP605 Hardware User Guide |

|

| UG526 (v1.1.1) February 1, 2010 |