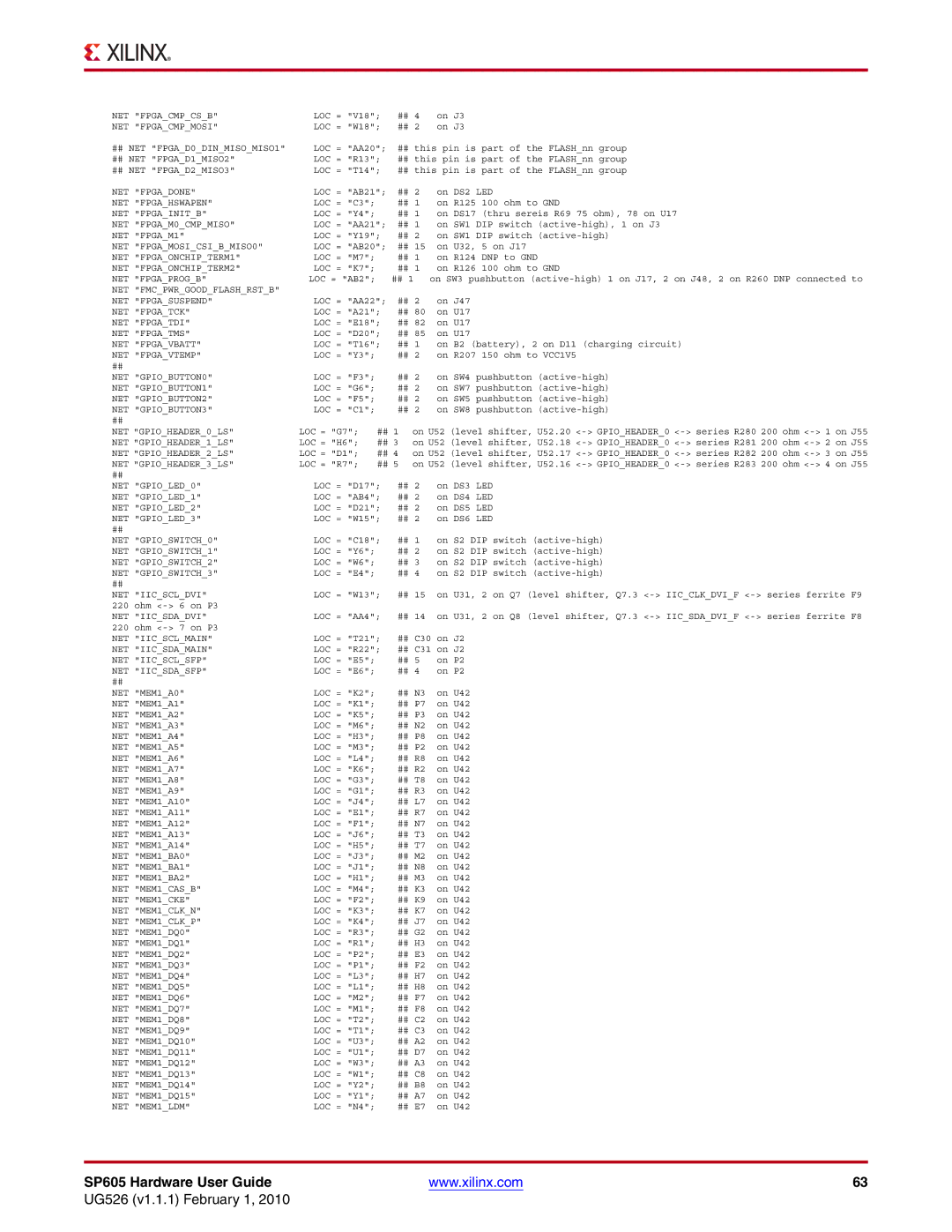

NET "FPGA_CMP_CS_B" | LOC = "V18"; | ## 4 | on J3 |

|

NET "FPGA_CMP_MOSI" | LOC = "W18"; | ## 2 | on J3 |

|

## NET "FPGA_D0_DIN_MISO_MISO1" | LOC = "AA20"; | ## this pin is | part of the FLASH_nn group | |

## NET "FPGA_D1_MISO2" | LOC = "R13"; | ## this pin is | part of the FLASH_nn group | |

## NET "FPGA_D2_MISO3" | LOC = "T14"; | ## this pin is | part of the FLASH_nn group | |

NET "FPGA_DONE" | LOC = "AB21"; | ## 2 | on DS2 LED | |

NET "FPGA_HSWAPEN" | LOC = "C3"; | ## 1 | on R125 | 100 ohm to GND |

NET "FPGA_INIT_B" | LOC = "Y4"; | ## 1 | on DS17 | (thru sereis R69 75 ohm), 78 on U17 |

NET "FPGA_M0_CMP_MISO" | LOC = "AA21"; | ## 1 | on SW1 DIP switch | |

NET "FPGA_M1" | LOC = "Y19"; | ## 2 | on SW1 DIP switch | |

NET "FPGA_MOSI_CSI_B_MISO0" | LOC = "AB20"; | ## 15 | on U32, | 5 on J17 |

NET "FPGA_ONCHIP_TERM1" | LOC = "M7"; | ## 1 | on R124 | DNP to GND |

NET "FPGA_ONCHIP_TERM2" | LOC = "K7"; | ## 1 | on R126 | 100 ohm to GND |

NET "FPGA_PROG_B" | LOC = "AB2"; | ## 1 | on SW3 pushbutton | |

NET "FMC_PWR_GOOD_FLASH_RST_B" |

|

|

|

|

NET "FPGA_SUSPEND" | LOC = "AA22"; | ## 2 | on J47 |

|

NET "FPGA_TCK" | LOC = "A21"; | ## 80 | on U17 |

|

NET "FPGA_TDI" | LOC = "E18"; | ## 82 | on U17 |

|

NET "FPGA_TMS" | LOC = "D20"; | ## 85 | on U17 |

|

NET "FPGA_VBATT" | LOC = "T16"; | ## 1 | on B2 (battery), 2 on D11 (charging circuit) | |

NET "FPGA_VTEMP" | LOC = "Y3"; | ## 2 | on R207 | 150 ohm to VCC1V5 |

## |

|

|

|

|

NET "GPIO_BUTTON0" | LOC = "F3"; | ## 2 | on SW4 pushbutton | |

NET "GPIO_BUTTON1" | LOC = "G6"; | ## 2 | on SW7 pushbutton | |

NET "GPIO_BUTTON2" | LOC = "F5"; | ## 2 | on SW5 pushbutton | |

NET "GPIO_BUTTON3" | LOC = "C1"; | ## 2 | on SW8 pushbutton | |

## |

|

|

|

|

|

|

NET "GPIO_HEADER_0_LS" | LOC = "G7"; | ## 1 | on U52 (level shifter, U52.20 | |||

NET "GPIO_HEADER_1_LS" | LOC = "H6"; | ## 3 | on U52 (level shifter, U52.18 | |||

NET "GPIO_HEADER_2_LS" | LOC = "D1"; | ## 4 | on U52 (level shifter, U52.17 | |||

NET "GPIO_HEADER_3_LS" | LOC = "R7"; | ## 5 | on U52 (level shifter, U52.16 | |||

## |

|

|

|

|

|

|

NET "GPIO_LED_0" | LOC = "D17"; | ## 2 | on DS3 LED | |||

NET "GPIO_LED_1" | LOC = "AB4"; | ## 2 | on DS4 LED | |||

NET "GPIO_LED_2" | LOC = "D21"; | ## 2 | on DS5 LED | |||

NET "GPIO_LED_3" | LOC = "W15"; | ## 2 | on DS6 LED | |||

## |

|

|

|

|

|

|

NET "GPIO_SWITCH_0" | LOC = "C18"; | ## 1 | on S2 DIP switch | |||

NET "GPIO_SWITCH_1" | LOC = "Y6"; |

| ## 2 | on S2 DIP switch | ||

NET "GPIO_SWITCH_2" | LOC = "W6"; |

| ## 3 | on S2 DIP switch | ||

NET "GPIO_SWITCH_3" | LOC = "E4"; |

| ## 4 | on S2 DIP switch | ||

## |

|

|

|

|

|

|

NET "IIC_SCL_DVI" | LOC = "W13"; | ## 15 | on U31, 2 on Q7 (level shifter, Q7.3 | |||

220 | ohm |

|

|

|

|

|

NET "IIC_SDA_DVI" | LOC = "AA4"; | ## 14 | on U31, 2 on Q8 (level shifter, Q7.3 | |||

220 | ohm |

|

|

|

|

|

NET "IIC_SCL_MAIN" | LOC = "T21"; | ## C30 | on J2 | |||

NET "IIC_SDA_MAIN" | LOC = "R22"; | ## C31 | on J2 | |||

NET "IIC_SCL_SFP" | LOC = "E5"; |

| ## 5 | on P2 | ||

NET "IIC_SDA_SFP" | LOC = "E6"; |

| ## 4 | on P2 | ||

## |

|

|

|

|

|

|

NET "MEM1_A0" | LOC = "K2"; |

| ## N3 | on U42 | ||

NET "MEM1_A1" | LOC = "K1"; |

| ## P7 | on U42 | ||

NET "MEM1_A2" | LOC = "K5"; |

| ## P3 | on U42 | ||

NET "MEM1_A3" | LOC = "M6"; |

| ## N2 | on U42 | ||

NET "MEM1_A4" | LOC = "H3"; |

| ## P8 | on U42 | ||

NET "MEM1_A5" | LOC = "M3"; |

| ## P2 | on U42 | ||

NET "MEM1_A6" | LOC = "L4"; |

| ## R8 | on U42 | ||

NET "MEM1_A7" | LOC = "K6"; |

| ## R2 | on U42 | ||

NET "MEM1_A8" | LOC = "G3"; |

| ## T8 | on U42 | ||

NET "MEM1_A9" | LOC = "G1"; |

| ## R3 | on U42 | ||

NET "MEM1_A10" | LOC = "J4"; |

| ## L7 | on U42 | ||

NET "MEM1_A11" | LOC = "E1"; |

| ## R7 | on U42 | ||

NET "MEM1_A12" | LOC = "F1"; |

| ## N7 | on U42 | ||

NET "MEM1_A13" | LOC = "J6"; |

| ## T3 | on U42 | ||

NET "MEM1_A14" | LOC = "H5"; |

| ## T7 | on U42 | ||

NET "MEM1_BA0" | LOC = "J3"; |

| ## M2 | on U42 | ||

NET "MEM1_BA1" | LOC = "J1"; |

| ## N8 | on U42 | ||

NET "MEM1_BA2" | LOC = "H1"; |

| ## M3 | on U42 | ||

NET "MEM1_CAS_B" | LOC = "M4"; |

| ## K3 | on U42 | ||

NET "MEM1_CKE" | LOC = "F2"; |

| ## K9 | on U42 | ||

NET "MEM1_CLK_N" | LOC = "K3"; |

| ## K7 | on U42 | ||

NET "MEM1_CLK_P" | LOC = "K4"; |

| ## J7 | on U42 | ||

NET "MEM1_DQ0" | LOC = "R3"; |

| ## G2 | on U42 | ||

NET "MEM1_DQ1" | LOC = "R1"; |

| ## H3 | on U42 | ||

NET "MEM1_DQ2" | LOC = "P2"; |

| ## E3 | on U42 | ||

NET "MEM1_DQ3" | LOC = "P1"; |

| ## F2 | on U42 | ||

NET "MEM1_DQ4" | LOC = "L3"; |

| ## H7 | on U42 | ||

NET "MEM1_DQ5" | LOC = "L1"; |

| ## H8 | on U42 | ||

NET "MEM1_DQ6" | LOC = "M2"; |

| ## F7 | on U42 | ||

NET "MEM1_DQ7" | LOC = "M1"; |

| ## F8 | on U42 | ||

NET "MEM1_DQ8" | LOC = "T2"; |

| ## C2 | on U42 | ||

NET "MEM1_DQ9" | LOC = "T1"; |

| ## C3 | on U42 | ||

NET "MEM1_DQ10" | LOC = "U3"; |

| ## A2 | on U42 | ||

NET "MEM1_DQ11" | LOC = "U1"; |

| ## D7 | on U42 | ||

NET "MEM1_DQ12" | LOC = "W3"; |

| ## A3 | on U42 | ||

NET "MEM1_DQ13" | LOC = "W1"; |

| ## C8 | on U42 | ||

NET "MEM1_DQ14" | LOC = "Y2"; |

| ## B8 | on U42 | ||

NET "MEM1_DQ15" | LOC = "Y1"; |

| ## A7 | on U42 | ||

NET "MEM1_LDM" | LOC = "N4"; |

| ## E7 | on U42 | ||

SP605 Hardware User Guide | www.xilinx.com | 63 |

UG526 (v1.1.1) February 1, 2010