Chapter 1: SP605 Evaluation Board

Table

U1 FPGA Pin | Schematic | Connected To | |||

Netname | Connection | Net Name | |||

|

| ||||

|

|

|

|

| |

R22 | IIC_SDA_MAIN | J2.C31, U4.5(1) | – | – | |

T21 | IIC_SCL_MAIN | J2.C30, U4.6(1) | – | – | |

AA4 | IIC_SDA_DVI | Q8.2, U31.14 | Q8.3, P3.7 | IIC_SDA_DVI_F | |

|

|

|

|

| |

W13 | IIC_SCL_DVI | Q7.2, U31.15 | Q7.3, P3.6 | IIC_CLK_DVI_F | |

|

|

|

|

| |

E6 | IIC_SDA_SFP | P2.4 | – | – | |

|

|

|

|

| |

E5 | IIC_SCL_SFP | P2.5 | – | – | |

|

|

|

|

|

Notes:

1.U4 IIC bus signals are resistively coupled with 0 ohm resistors

2.Legend

J2, FMC LPC Connector P2, SFP Module Connector P3, DVI Connector

Qn.n,

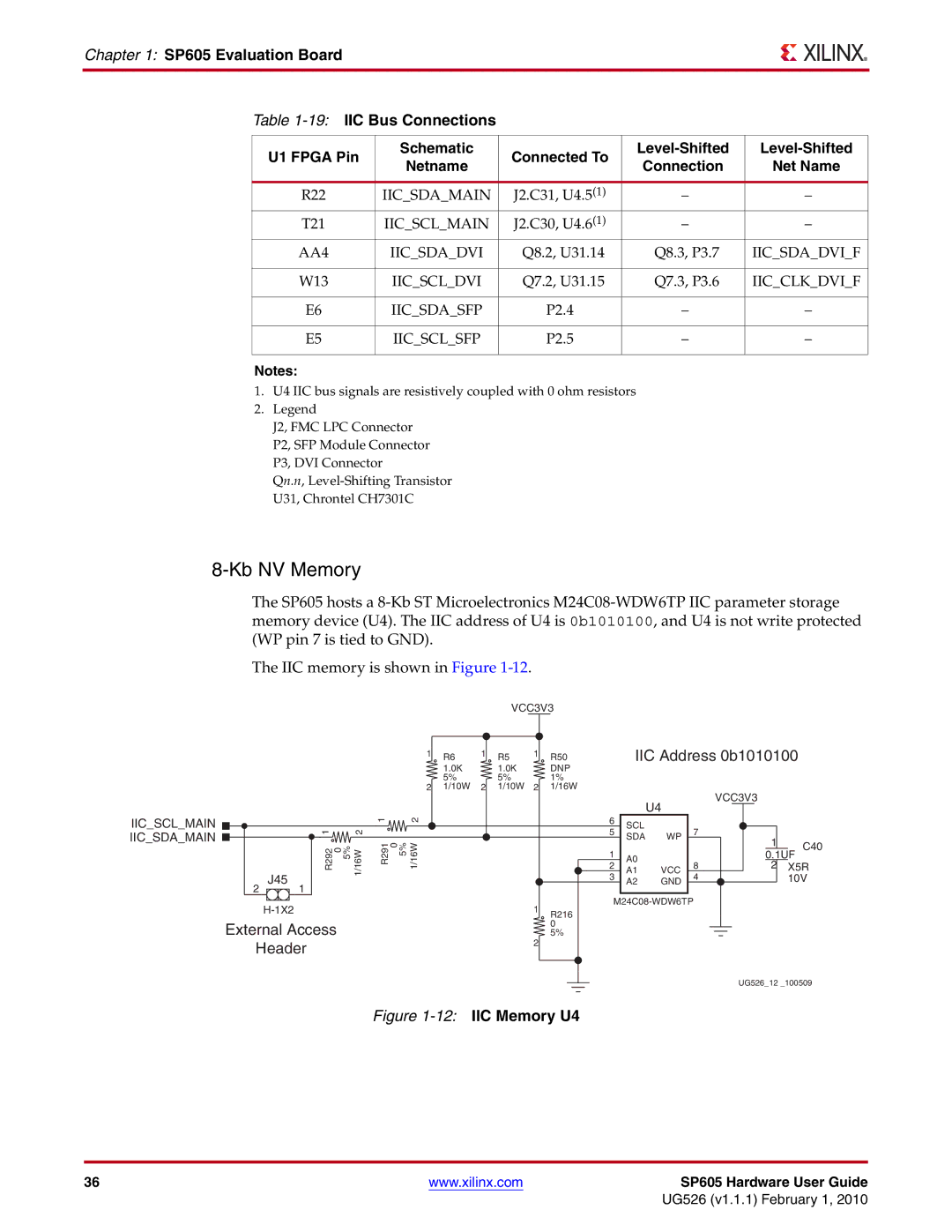

8-Kb NV Memory

The SP605 hosts a

The IIC memory is shown in Figure

VCC3V3

1 | R6 | 1 | R5 | 1 | R50 |

IIC Address 0b1010100

|

|

|

|

|

|

|

|

| 1.0K |

| 1.0K |

| DNP |

|

|

|

|

|

|

|

|

|

|

|

|

|

| 5% |

| 5% |

| 1% |

|

|

|

|

|

|

|

|

|

|

|

|

| 2 | 1/10W | 2 | 1/10W | 2 | 1/16W |

|

|

| VCC3V3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| U4 |

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

IIC_SCL_MAIN |

|

|

|

| 1 |

|

| 2 |

|

|

|

| 6 | SCL |

|

|

|

|

1 |

|

| 2 |

|

|

|

|

|

|

|

|

| 7 |

|

| |||

IIC_SDA_MAIN |

|

|

|

|

|

|

|

|

|

| 5 | SDA | WP | 1 |

| |||

|

| 5% |

| R291 | 0 | 5% | 1/16W |

|

|

|

|

|

| C40 | ||||

| R292 | 0 | 1/16W |

|

|

|

|

|

|

|

| |||||||

|

|

|

|

| 1 |

|

|

|

| |||||||||

|

|

|

|

| A0 |

|

| 0.1UF | ||||||||||

|

|

|

|

| 2 |

| 8 | 2 | X5R | |||||||||

|

|

|

|

| A1 | VCC | ||||||||||||

2 | J45 |

|

|

|

|

|

|

|

|

|

|

| 3 | A2 | GND | 4 |

| 10V |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

| 1 |

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

| R216 |

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

External Access |

|

|

|

|

|

|

|

|

|

| 0 |

|

|

|

|

| ||

|

|

|

|

|

|

|

|

| 2 | 5% |

|

|

|

|

| |||

Header |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| UG526_12 _100509 | |

Figure 1-12: IIC Memory U4

36 | www.xilinx.com | SP605 Hardware User Guide |

UG526 (v1.1.1) February 1, 2010