Chapter 1: SP605 Evaluation Board

3. SPI x4 Flash

The Xilinx

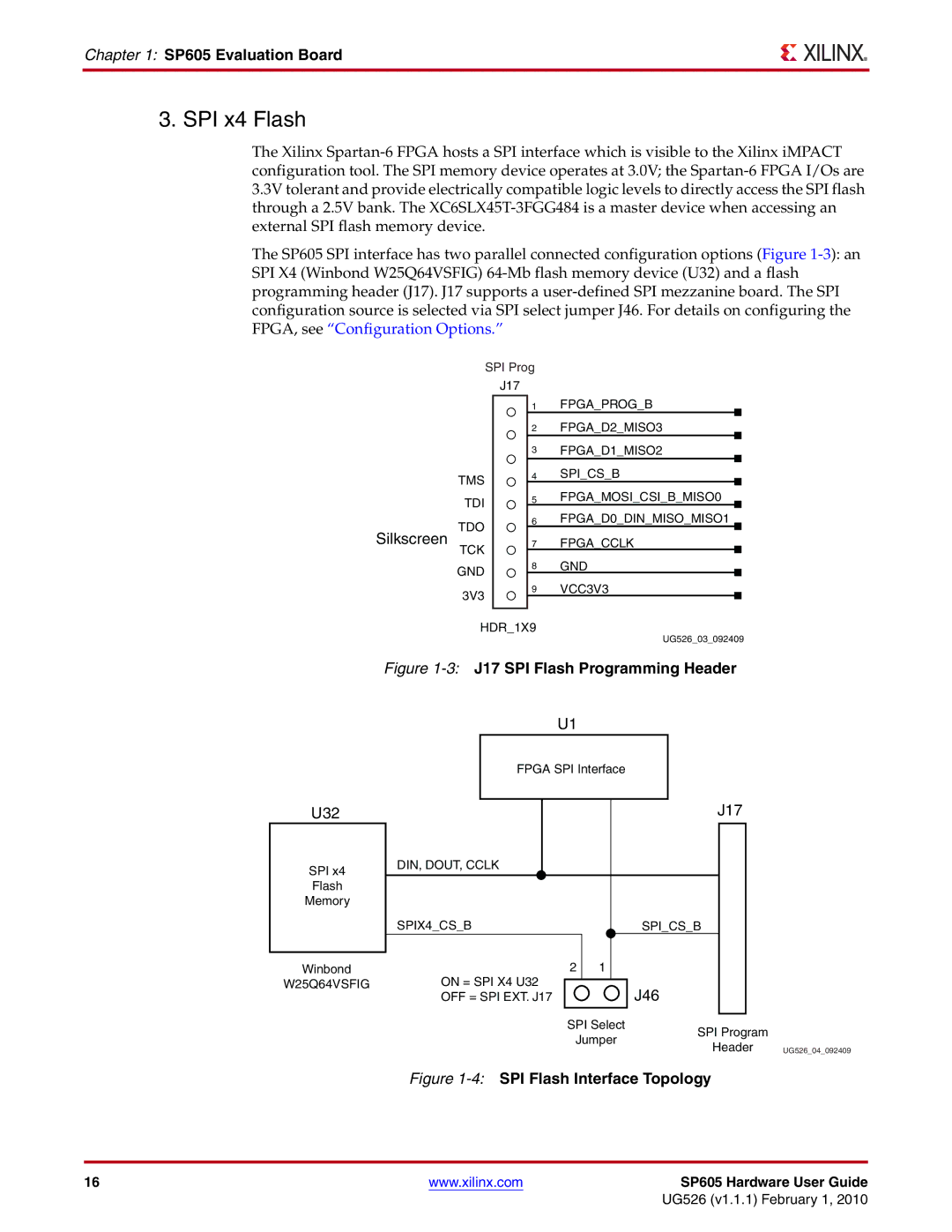

The SP605 SPI interface has two parallel connected configuration options (Figure

|

| SPI Prog |

|

|

| ||

|

|

| J17 |

|

|

| |

|

|

|

| 1 | FPGA_PROG_B |

|

|

|

|

|

| 2 | FPGA_D2_MISO3 |

| |

|

|

|

| 3 | FPGA_D1_MISO2 |

|

|

| TMS |

|

| 4 | SPI_CS_B |

|

|

| TDI |

|

| 5 | FPGA_MOSI_CSI_B_MISO0 |

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

| TDO |

|

| 6 | FPGA_D0_DIN_MISO_MISO1 | ||

Silkscreen |

|

| 7 | FPGA_CCLK |

|

| |

TCK |

|

|

|

| |||

|

|

| 8 | GND |

|

| |

| GND |

|

|

|

| ||

| 3V3 |

|

| 9 | VCC3V3 |

|

|

|

|

|

|

| |||

|

|

|

|

|

|

| |

|

|

|

|

|

|

| |

| HDR_1X9 | UG526_03_092409 | |||||

|

|

|

|

| |||

Figure 1-3: J17 SPI Flash Programming Header

U1

FPGA SPI Interface

U32

SPI x4

Flash

Memory

Winbond

W25Q64VSFIG

J17

DIN, DOUT, CCLK |

|

|

|

| |

|

|

|

|

| |

SPIX4_CS_B |

|

| SPI_CS_B |

| |

| 1 |

|

|

| |

2 |

|

|

| ||

ON = SPI X4 U32 |

|

|

| J46 |

|

|

|

|

| ||

OFF = SPI EXT. J17 |

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

SPI Select

SPI Program

Jumper

Header UG526_04_092409

Figure 1-4: SPI Flash Interface Topology

16 | www.xilinx.com | SP605 Hardware User Guide |

|

| UG526 (v1.1.1) February 1, 2010 |