Detailed Description

11. 10/100/1000 Tri-Speed Ethernet PHY

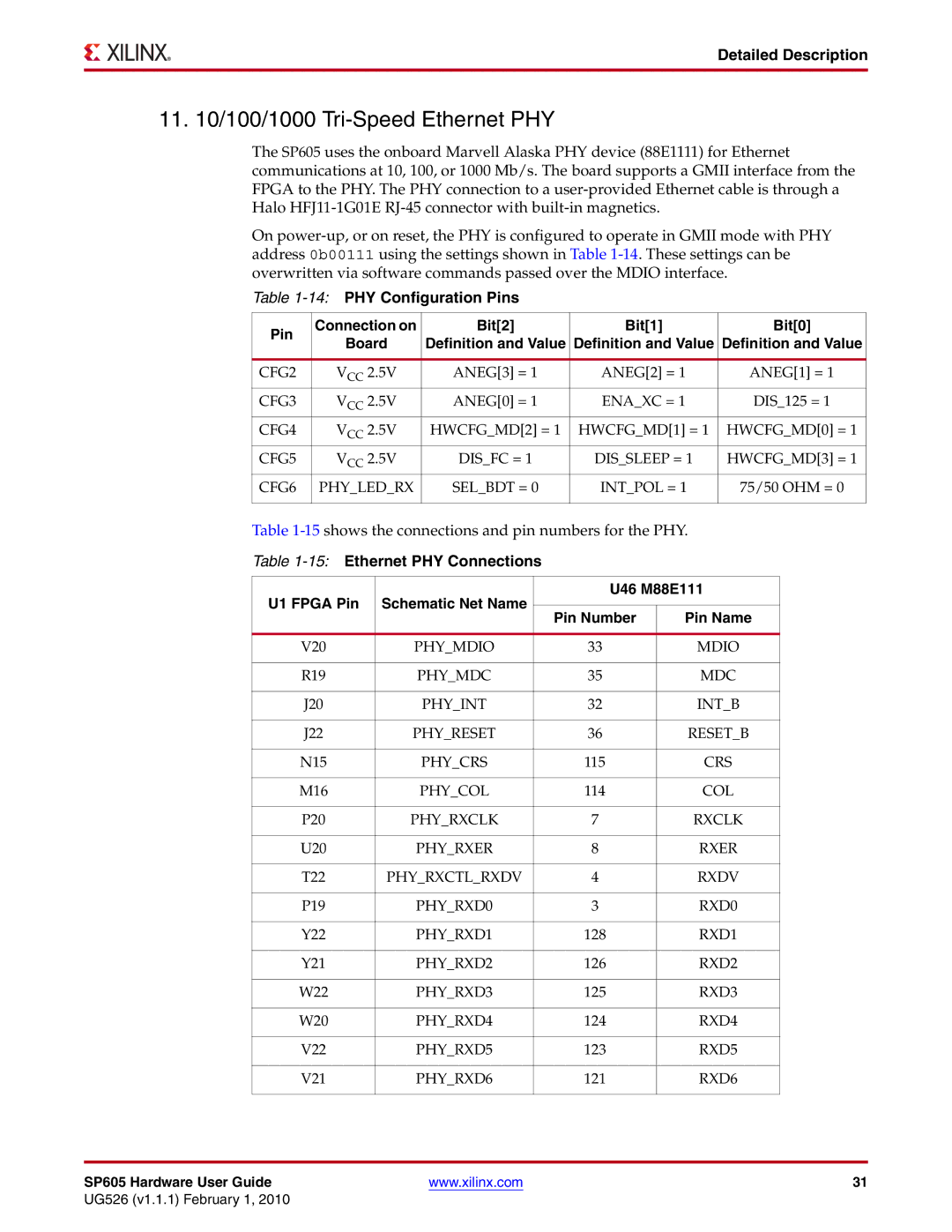

The SP605 uses the onboard Marvell Alaska PHY device (88E1111) for Ethernet communications at 10, 100, or 1000 Mb/s. The board supports a GMII interface from the FPGA to the PHY. The PHY connection to a

On

Table 1-14: PHY Configuration Pins

Pin | Connection on | Bit[2] | Bit[1] | Bit[0] | |

Board | Definition and Value | Definition and Value | Definition and Value | ||

| |||||

|

|

|

|

| |

CFG2 | VCC 2.5V | ANEG[3] = 1 | ANEG[2] = 1 | ANEG[1] = 1 | |

CFG3 | VCC 2.5V | ANEG[0] = 1 | ENA_XC = 1 | DIS_125 = 1 | |

CFG4 | VCC 2.5V | HWCFG_MD[2] = 1 | HWCFG_MD[1] = 1 | HWCFG_MD[0] = 1 | |

CFG5 | VCC 2.5V | DIS_FC = 1 | DIS_SLEEP = 1 | HWCFG_MD[3] = 1 | |

CFG6 | PHY_LED_RX | SEL_BDT = 0 | INT_POL = 1 | 75/50 OHM = 0 | |

|

|

|

|

|

Table

Table 1-15: Ethernet PHY Connections

U1 FPGA Pin | Schematic Net Name | U46 M88E111 | ||

|

| |||

Pin Number | Pin Name | |||

|

| |||

|

|

|

| |

V20 | PHY_MDIO | 33 | MDIO | |

|

|

|

| |

R19 | PHY_MDC | 35 | MDC | |

|

|

|

| |

J20 | PHY_INT | 32 | INT_B | |

|

|

|

| |

J22 | PHY_RESET | 36 | RESET_B | |

|

|

|

| |

N15 | PHY_CRS | 115 | CRS | |

|

|

|

| |

M16 | PHY_COL | 114 | COL | |

|

|

|

| |

P20 | PHY_RXCLK | 7 | RXCLK | |

|

|

|

| |

U20 | PHY_RXER | 8 | RXER | |

|

|

|

| |

T22 | PHY_RXCTL_RXDV | 4 | RXDV | |

|

|

|

| |

P19 | PHY_RXD0 | 3 | RXD0 | |

|

|

|

| |

Y22 | PHY_RXD1 | 128 | RXD1 | |

|

|

|

| |

Y21 | PHY_RXD2 | 126 | RXD2 | |

|

|

|

| |

W22 | PHY_RXD3 | 125 | RXD3 | |

|

|

|

| |

W20 | PHY_RXD4 | 124 | RXD4 | |

|

|

|

| |

V22 | PHY_RXD5 | 123 | RXD5 | |

|

|

|

| |

V21 | PHY_RXD6 | 121 | RXD6 | |

|

|

|

| |

SP605 Hardware User Guide | www.xilinx.com | 31 |

UG526 (v1.1.1) February 1, 2010