TMS320C25

TMS320C25-50

SPRS010B Ð MAY 1987 Ð REVISED NOVEMBER 1990

|

|

|

|

|

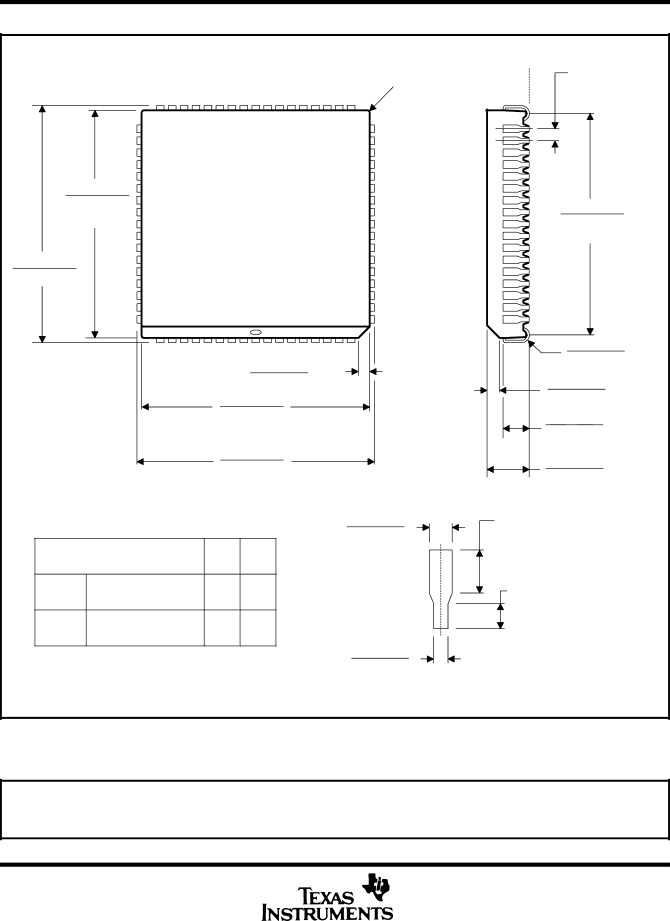

| Seating |

| |

|

|

|

|

|

| Plane | 1,27 (0.050) T.P. | |

|

|

|

|

|

|

| ||

|

|

|

|

| 0,25 (0.010) R Max |

| (see Note B) | |

|

|

|

|

|

|

|

| |

|

|

|

|

| 3 Places |

|

|

|

| 24,33 (0.956) |

|

|

|

|

|

| |

| 24,13 (0.950) |

|

|

|

| 23,62 (0.930) | ||

| (see Note A) |

|

|

|

| |||

|

|

|

|

| 23,11 (0.910) | |||

|

|

|

|

|

|

| ||

|

|

|

|

|

|

| (At Seating Plane) | |

| 25,27 (0.995) |

|

|

|

|

|

|

|

| 25,02 (0.985) |

|

|

|

|

|

|

|

ADVANCE |

|

|

|

|

|

| 0,94 (0.037) | |

|

|

| 1,22 (0.048) |

|

| 0,69 (0.027) R | ||

|

|

| ⋅ 45° |

|

|

| ||

|

|

| 1,07 (0.042) |

| 1,35 (0.053) | ⋅ 45° | ||

|

| 24,33 (0.956) |

|

| 1,19 (0.047) | |||

|

|

|

|

| ||||

INFORMATION |

|

| 24,13 (0.950) |

|

| 2,79 (0.110) |

| |

|

| (see Note A) |

|

|

| |||

|

|

|

| 2,41 (0.095) |

| |||

|

|

|

|

|

|

| ||

|

| 25,27 (0.995) |

|

| 4,50 (0.177) |

| ||

|

| 25,02 (0.985) |

|

|

| |||

|

|

|

| 4,24 (0.167) |

| |||

|

|

|

|

|

|

| ||

Thermal Resistance Characteristics | 0,81 (0.032) | 1,52 (0.060) |

| |||||

0,66 (0.026) | Min |

|

| |||||

|

|

|

|

|

| |||

| PARAMETER | MAX | UNIT |

|

|

|

| |

RθJA | 46 | °C/W |

| 0,64 (0.025) |

| |||

|

|

| ||||||

| thermal resistance |

|

| |||||

|

|

|

|

|

| Min |

|

|

| RθJC | 11 | °C/W |

|

|

|

| |

| thermal resistance |

|

|

|

| |||

|

|

|

|

| 0,51 (0.020) |

|

|

|

|

|

|

|

| 0,36 (0.014) |

|

|

|

|

|

|

|

| Lead Detail |

|

|

|

|

| ALL LINEAR DIMENSIONS ARE IN MILLIMETERS AND PARENTHETICALLY IN INCHES |

| |||||

NOTES: A. Centerline of center pin, each side, is within 0,10 (0.004) of package centerline as determined by this dimension. B. Location of each pin is within 0,127 (0.005) of true position with respect to center pin on each side.

WARNING

When reflow soldering is required, refer to page 54 for special handling instructions.

56 | POST OFFICE BOX 1443 • HOUSTON, TEXAS 77001 |