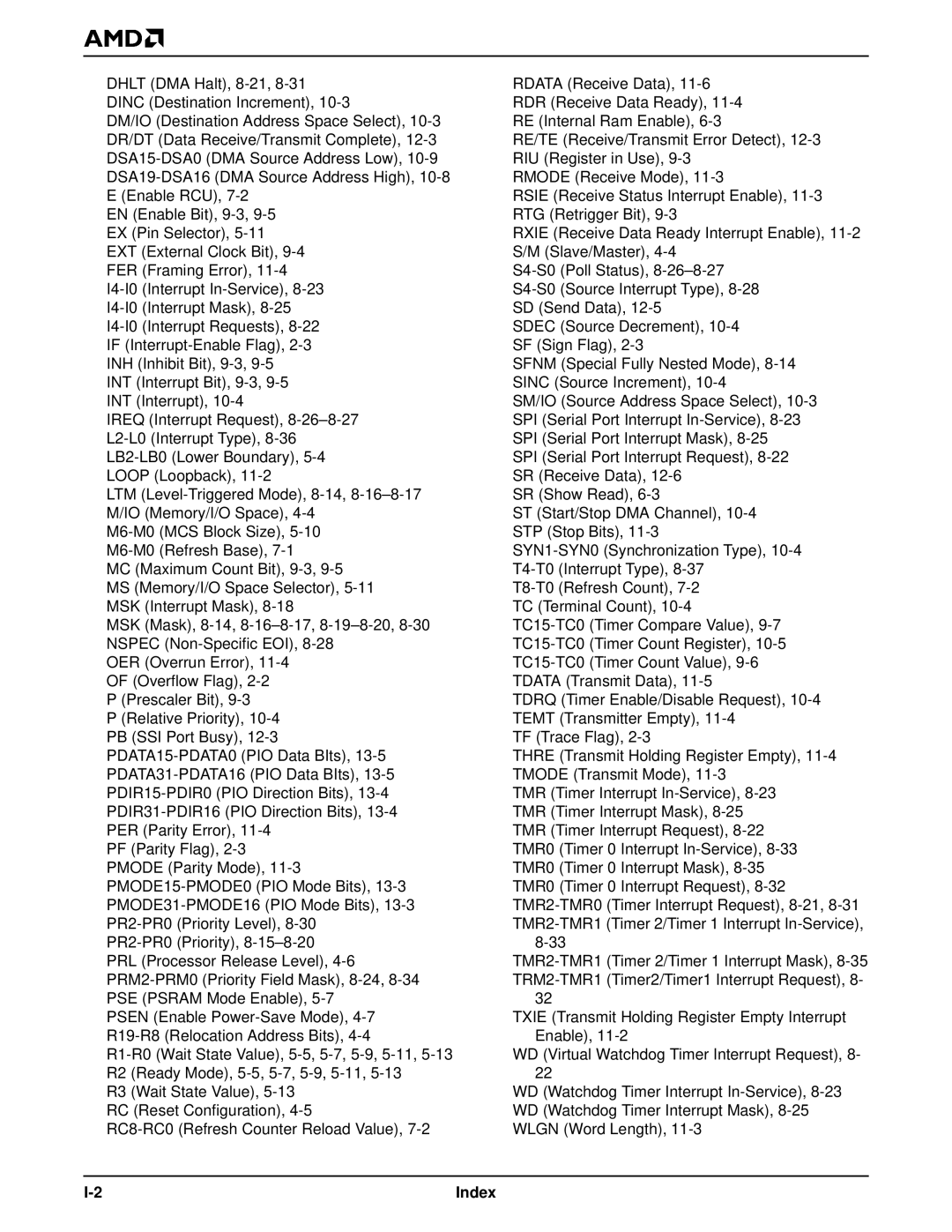

DHLT (DMA Halt), | RDATA (Receive Data), |

DINC (Destination Increment), | RDR (Receive Data Ready), |

DM/IO (Destination Address Space Select), | RE (Internal Ram Enable), |

DR/DT (Data Receive/Transmit Complete), | RE/TE (Receive/Transmit Error Detect), |

RIU (Register in Use), | |

RMODE (Receive Mode), | |

E (Enable RCU), | RSIE (Receive Status Interrupt Enable), |

EN (Enable Bit), | RTG (Retrigger Bit), |

EX (Pin Selector), | RXIE (Receive Data Ready Interrupt Enable), |

EXT (External Clock Bit), | S/M (Slave/Master), |

FER (Framing Error), | |

SD (Send Data), | |

SDEC (Source Decrement), | |

IF | SF (Sign Flag), |

INH (Inhibit Bit), | SFNM (Special Fully Nested Mode), |

INT (Interrupt Bit), | SINC (Source Increment), |

INT (Interrupt), | SM/IO (Source Address Space Select), |

IREQ (Interrupt Request), | SPI (Serial Port Interrupt |

SPI (Serial Port Interrupt Mask), | |

SPI (Serial Port Interrupt Request), | |

LOOP (Loopback), | SR (Receive Data), |

LTM | SR (Show Read), |

M/IO (Memory/I/O Space), | ST (Start/Stop DMA Channel), |

STP (Stop Bits), | |

MC (Maximum Count Bit), | |

MS (Memory/I/O Space Selector), | |

MSK (Interrupt Mask), | TC (Terminal Count), |

MSK (Mask), | |

NSPEC | |

OER (Overrun Error), | |

OF (Overflow Flag), | TDATA (Transmit Data), |

P (Prescaler Bit), | TDRQ (Timer Enable/Disable Request), |

P (Relative Priority), | TEMT (Transmitter Empty), |

PB (SSI Port Busy), | TF (Trace Flag), |

THRE (Transmit Holding Register Empty), | |

TMODE (Transmit Mode), | |

TMR (Timer Interrupt | |

TMR (Timer Interrupt Mask), | |

PER (Parity Error), | TMR (Timer Interrupt Request), |

PF (Parity Flag), | TMR0 (Timer 0 Interrupt |

PMODE (Parity Mode), | TMR0 (Timer 0 Interrupt Mask), |

TMR0 (Timer 0 Interrupt Request), | |

PRL (Processor Release Level), | |

PSE (PSRAM Mode Enable), | 32 |

PSEN (Enable | TXIE (Transmit Holding Register Empty Interrupt |

Enable), | |

WD (Virtual Watchdog Timer Interrupt Request), 8- | |

R2 (Ready Mode), | 22 |

R3 (Wait State Value), | WD (Watchdog Timer Interrupt |

RC (Reset Configuration), | WD (Watchdog Timer Interrupt Mask), |

WLGN (Word Length), |

Index |