SP Switch Router Adapter Guide

Lucent Technologies

Contents

Chapter Configuring the SP Switch Router Adapter

Chapter

Appendix a Part Numbers

Appendix C

Viii SP Switch Router Adapter Guide 1.4 Update

Figures

Figures

Tables

Tables

About 1.4 Update

How to use this Guide

Manual sets

SP Switch Router manuals

IBM SP system manuals

Documentation conventions

Convention Meaning

IP routing publications

Introduction to the SP Switch Router Adapter card

What is the RS/6000 SP Switch Router ?

SP Switch Router

SP Switch cable

SP Switch Router systems for IBM sites

Cables included in your system

Pcmcia 520MB disk

Redundant AC power supplies

Redundant supply safety

Ethernet cable

Upgrading system memory

RAM

Overview of the SP Switch Router Adapter card

Face plate diagram

Inserting a media card into the SP Switch Router

Media card components

Card insertion procedure

ESD requirements

OFF Error

SP Switch Router Adapter card LEDs

LED activity during boot

OFF

TX HB

LED activity during normal operations

STATE1 Bottom two LEDs amber go on during

SP Switch Router Adapter card specifications

Element Value

Assigning filters

Tcpdump

Snmp on the SP Switch Router Adapter card

SP Switch Router Adapter dependent node MIB support

SP Switch Router Adapter media card states Snmp

Snmp configuration overview

Snmp activity during media card start up

Configuring the SP Switch Router Adapter

Introduction to installation and configuration

Pre-installation assumptions

Location of relevant information

Order of information

Installing an SP Switch Router Adapter card

Installation overview

Installing the Pcmcia spinning disk

Managing Pcmcia slots

Installation steps

Panic dumps sent to external flash device

file entries should now look like the following

Save all changes and reboot

Do not damage the connector ends

Attaching SP Switch Router cables

SP switch cable

Ethernet cable

Procedure for attaching cables to card and SP Switch

Keep the plastic cap on

Determining the switch connection for a dependent node

Configuration required on the SP system

Procedure

Sources of configuration information

Multiple frames for multiple system connections

SP system a

Configuration files and their uses

Step-by-step media card configuration

Overview of steps

SP Switch Router requires a specific configuration file

Check Snmp in the SP Switch Router system

Members

Unspecified Subagents

Put Snmp changes into effect

ALL GET SET Trap

Method 1 Recommended, use SP Snmp Manager

Assign IP addresses

Method 2 Optional, edit /etc/grifconfig.conf

Netmask

Interface name

Internet address

Broadcast / destination address

Argument field

Default MTU values

Putting grifconfig.conf additions into effect

MTU discovery facility

Specify card-level parameters Card profile

Change profile settings

Specify Icmp throttling

Specify different dump settings

Specify different executables

Configuring the SP Switch Router Adapter

Look at the SP Switch Router Adapter card settings

Change executables for all dev1 cards Load profile

Change dump defaults for all dev1 cards Dump profile

Dump vectors read-only

Configuring the SP Switch Router Adapter

Run dev1config to create grdev1.conf

How to run the command

Method 2 Optional, edit /etc/grdev1.conf

Contents of /etc/grdev1.conf

Parameter definitions

Extension Node Identifier ibmSPDepNodeName read-only

Configuration State ibmSPDepConfigState read-only

Reset card to install files

Saving configuration files

Verify SP Switch Router Adapter card from router

Verify media card operation using ping

Check media card status using grcard

Verify switch node connectivity using ping

Media card states

Reset media card using grreset

# grreset all -h # grreset slot -h

Checking connectivity to the SP system

Procedure

Configuring the SP Switch Router Adapter

Monitoring and Management Tools

Csconfig

SP Switch Router command overview

flashcmd

Grcard

Getver

Grarp

Grfins

Grrmb

Grreset

Grms

Grroute

Mountf

Grstat

Grwrite

Setver

Ping

SP Switch Router Unix tools

Route

Traceroute

Grroute.conf file

Using the netstat command

Netstat -rn

Netstat -rs

Netstat -in

Netstat -an

Netstat -s

Layer 3 statistics

Obtaining layer 2 and 3 statistics grstat

Options

List of IP stats

Multicast packets attempted to route

Layer 2 statistics

List of layer 2 stats

SP Switch Router Adapter card maint commands

Preparing to use maint commands

Find transmit tx binary version maint

Sample maint commands

Find hardware and software version numbers maint

Display configuration and status maint

Maint 5 display switch statistics

Maint 4 display media statistics

Filtering commands maint 50-58

Maint 6 display combus statistics

List the filters per media card maint

List where filters are assigned maint

Configure UDP packet discards maint 89

Display ARP table maint 189

Flush the ARP cache maint 189

Display switch route table maint 189

Switch route not found

Where to find the user guide

Checking for hardware problems grdiag

What is tested

Stopping or halting grdiag

When a media card does not boot after grdiag

Switch receive error can indicate hardware problem

Media card dumps

SP Switch Router dumps

System dumps

Use grdinfo to collect logs

Data collection utility grdinfo

Grdinfo -card=slot all

SP Switch Router example

Grdinfo -all

============================================================

Monitoring and Management Tools

Monitoring and Management Tools

SP Switch Router logs

Accessing a log file

Sample gr.console log

For example

Sample gr.boot log

Sample entries in the gr.boot log

Sample messages log

Sample entries in the messages log

Burning in media card flash memory

Part Numbers

Parts list model 04S

GRF-AC-CB16

Parts list model 16S

GRF-AC-SWB16

GRF-AC-AC16

Publication numbers IBM manuals

IBM publication number Manual title

Log Messages

Alphabetical list of messages

Log Messages

Message descriptions

Access Fifo Sync Error from RC, int1=%d

Access Fifo Sync Error from TC, int1=%d

ACK Words 0x%08x, 0x%08x, 0x%08x, 0x%08x, 0x%08x, 0x%08x

Bad Hdr/Svc received, Ret code=%d

ARP added IP= %s, SW-node=%d, state=%d

Board Configuration timed-out, retrying

Configuring transmit side

Configuration Parameters

CPU ready msg received from TX-CPU

Discarding msg, unknown msgtype 0x%x

Descriptor Sync Error from RC, int1=%d

Descriptor Sync Error from TC, int1=%d

ERR! Duplicated buffer %d

Hot interrupt detected, ier1=0x%8x, ier2=0x8x

Expect Nodeinit but received Stat/Err Request

Expired IP buffer received %d

Initializing Main Task

Loopback routes found for IP adr 0x%x, sw-node

IOSTB3RX SET TOD service message received

Initializing RX Subsystem data structure

Lost of STI clock, Tbic Status = 0x%x

RX Clock is valid

NetStar GigaRouter %s RX Interface Initializing

NetStar GigaRouter %s TX Interface Initializing

RX-CPU Loaded msg received from TX-CPU

RX-TBIC permanent errors detected IER1=0x%x, IER2=0x%x

RX send Sendtod to the switch. or RX Reading TBICs TOD

RX-TBIC outage errors detected IER1=0x%x, IER2=0x%x

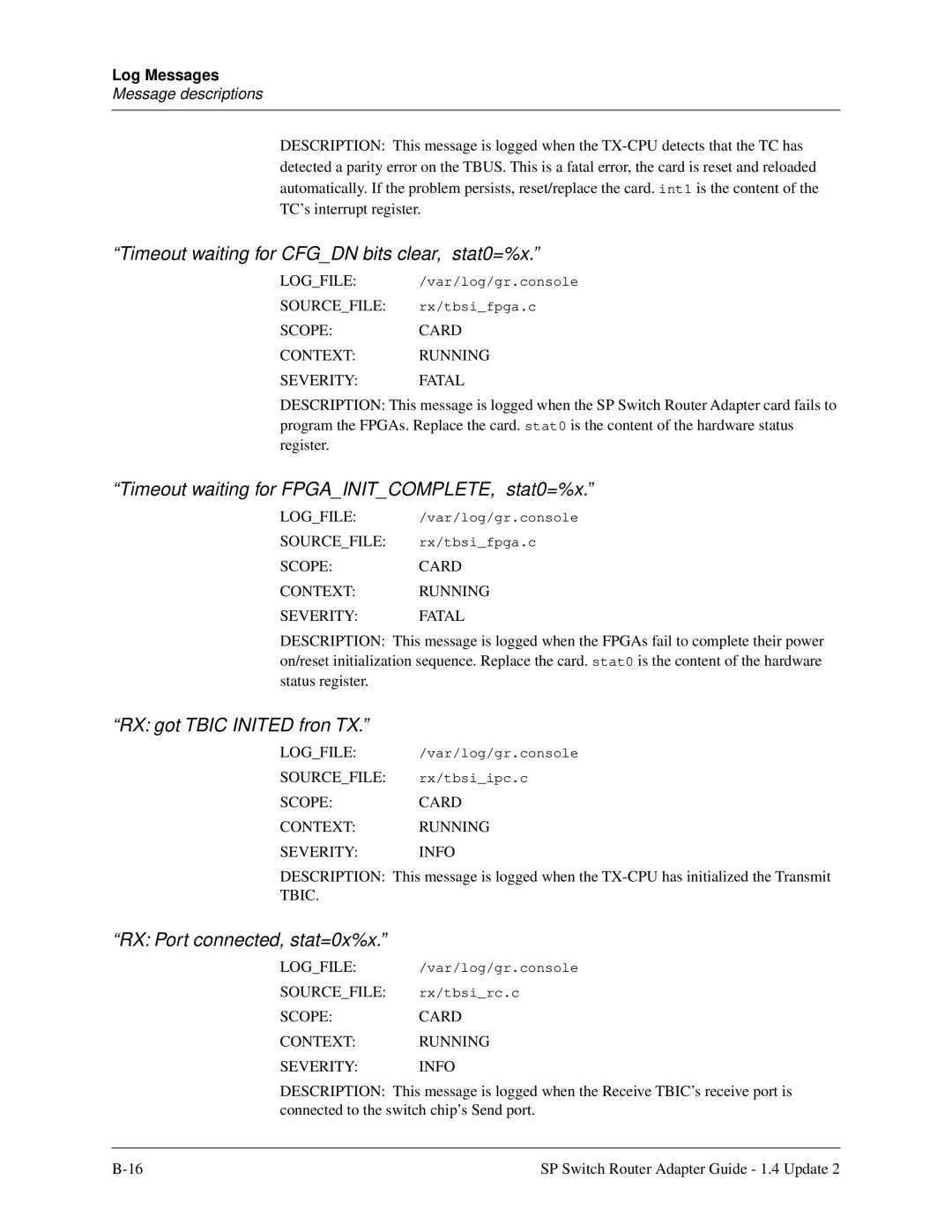

RX got Tbic Inited fron TX

Sending if Reset message to TX-CPU

RX-TBIC transientt errors detected IER1=0x%x, IER2=0x%x

Send TOD service message received

Sending Grid Init Sending if Init for if 0x%x

Sending params to TX

Sending mib-2 trap, type = %d, state = %d

State machine changes from xxx to yyy

Switch route entry not found, node = %d

Status/Err service message received

Switch received with errors. Descriptor 0x%8x

Svc Msg rxed, svccmd=0x%x %s, nodecmd 0x%x %s

TB4 segment received in wrong state

Switch Route table loaded, %d entries

TB4 segment received in error. TB4-HDR word%d 0x%x

Tbic Init msg sent to TX-CPU

TBSI-RX TBICs TOD 0x%x, 0x%x

Tbus Parity Error from RC, int1=%d

Tbus Parity Error from TC, int1=%d

TBSI-TX Unexpected SVC threshold interrupt

Timeout waiting for Cfgdn bits clear, stat0=%x

Timeout waiting for FPGAINITCOMPLETE, stat0=%x

Timed out resolving ARP. If %d IP %d.%d.%d.%d

RX Setting the RC in operational mode, stat=0x%x

TX-CPU Access Fifo busy, discarding IP packet

TX-CPU Config Params msg received from RX-CPU

TX-PROR startnode %d, endnode %d, # entries %d

TX-CPU Tbic Init msg received from RX-CPU

TX Port is connected, stat=0x%x

TX pseudo STI clock is valid

TX-TBIC transient errors detected IER1=0x%x, IER2=0x%x

TX-TBIC outage errors detected IER1=0x%x, IER2=0x%x

TX-TBIC permanent errors detected IER1=0x%x, IER2=0x%x

Un-expected descriptor from RC, desctype=%d

Log Messages

Network Configuration Examples

Configuration requirements

Example 2 Multiple cards, single partition

ARP table

Incoming traffic going to SP processor nodes

Configuration tasks

Outgoing traffic coming from SP processor nodes

Recovery procedure if an SP Switch Router Adapter card fails

Example 3 Multiple cards, multiple SP partitions

Support for code installation

SP Switch Router as an IBM product

Obtaining new machine code

IBM License Agreement for Machine Code

Index

ARP

Index

GRF

IBM

Index

MTU

Snmp

Index

Index