Description

Features

Applications

Ordering Information

Product Preview DS21Q55

Ansi

Clock Synthesizer

Feature Highlights

General

Line Interface

System Interface

Framer/Formatter

Control Port

Test and Diagnostics

Hdlc Controllers

Extended System Information Bus

Product Preview DS21Q55 012103

Table of Contents

Channel Blocking Registers

Error Count Registers

Signaling Operation

PER-CHANNEL Idle Code Generation

186

149

170

177

Mechanical Descriptions

AC Timing Parameters and Diagrams

Operating Parameters

Document Revision History

Block Diagram Figure

Block Diagram

PIN Function Description

Transmit Side Pins

Input/Output

Transmit Signaling Input

TSYNCx

Transmit Sync

Receive Side Pins

Receive Sync

Receive Signaling Output

Receive Signaling Freeze

RSYNCx

Tstrst

Parallel Control Port Pins

INT

BTS

MUX

Jtms

Jtag Test Access Port Pins

A7/ALEAS

Jtrst

Line Interface Pins

Supply Pins

Pinout DS21Q55 PIN Description Table

PIN Symbol Type Description

ESIBRD2

DVSS3

DVSS4

ESIBRD1

RLCLK1

RFSYNC2

RFSYNC3

RFSYNC4

RSYNC2

RSIGF3

RSIGF4

RSYNC1

TNEGI2

TLINK3

TLINK4

TNEGI1

TVSS4

TVSS2

TVSS3

AD1

Package DS21Q55 Pin DIAGRAM, 27mm BGA

Address Register Name Abbreviation

Parallel Port

Register Map

PCDR1

SR9

IMR9

Pcpr

RS4

RS1

RS2

RS3

H1FC

TCBR3

TCBR4

H1TC

RAF

RFDLM1

RFDLM2

Iboc

Information

Rsaoics Rsrcs Rfcs Brcs Thscs Peics Tfcs Btcs

Special PER-CHANNEL Register Operation

Register Name

Pcpr

PCDR4

PCDR1

PCDR2

PCDR3

Programming Sequence Figure

Programming Model

Mstrreg

Power-Up Sequence

Master Mode Register

TEST1 TEST0 Effect on Output Pins

Status Registers

Interrupt Handling

IIR2

Information Registers

Interrupt Information Registers

IIR1

Transmit Clock Source

Clock MAP

Clock MAP Figure

OOF2 OOF1 OUT of Frame Criteria

T1 FRAMER/FORMATTER Control Registers

T1 Control Registers

T1RCR1

T1RCR2

Bit 1/Receive Japanese CRC6 Enable RJC

Bit 5/Receive B8ZS Enable RB8ZS = B8ZS disabled

Bit 6/Receive Frame Mode Select RFM = D4 framing mode

T1TCR1

TB8ZS TSLC96 Tzse FBCT2 FBCT1 TD4YM Tzbtsi TB7ZS

Bit 7/Transmit B8ZS Enable TB8ZS = B8ZS disabled

T1TCR2

06h

07h

Bit 2/Transmit Frame Mode Select TFM = D4 framing mode

T1CCR1

T1 Common Control Register

T1 Receive-Side Digital-Milliwatt Code Generation

T1 Transmit Transparency

T1RDMR3

T1RDMR1

T1RDMR2

10h

T1 Information Register

INFO1

Information Register

Yellow Alarm RAI

T1 Alarm Criteria Table

Alarm SET Criteria Clear Criteria

E1RCR1

E1 FRAMER/FORMATTER Control Registers

E1 Control Registers

Rcla

E1 SYNC/RESYNC Criteria Table

E1RCR2

34h

E1TCR1

E1TCR2

Bit 0/Automatic Remote Alarm Generation ARA = disabled

Bit 1/Automatic AIS Generation Aais = disabled

Bit 2/Automatic E-Bit Enable Aebe

Automatic Alarm Generation

INFO7

E1 Information Registers

INFO3

E1 Alarm Criteria Table

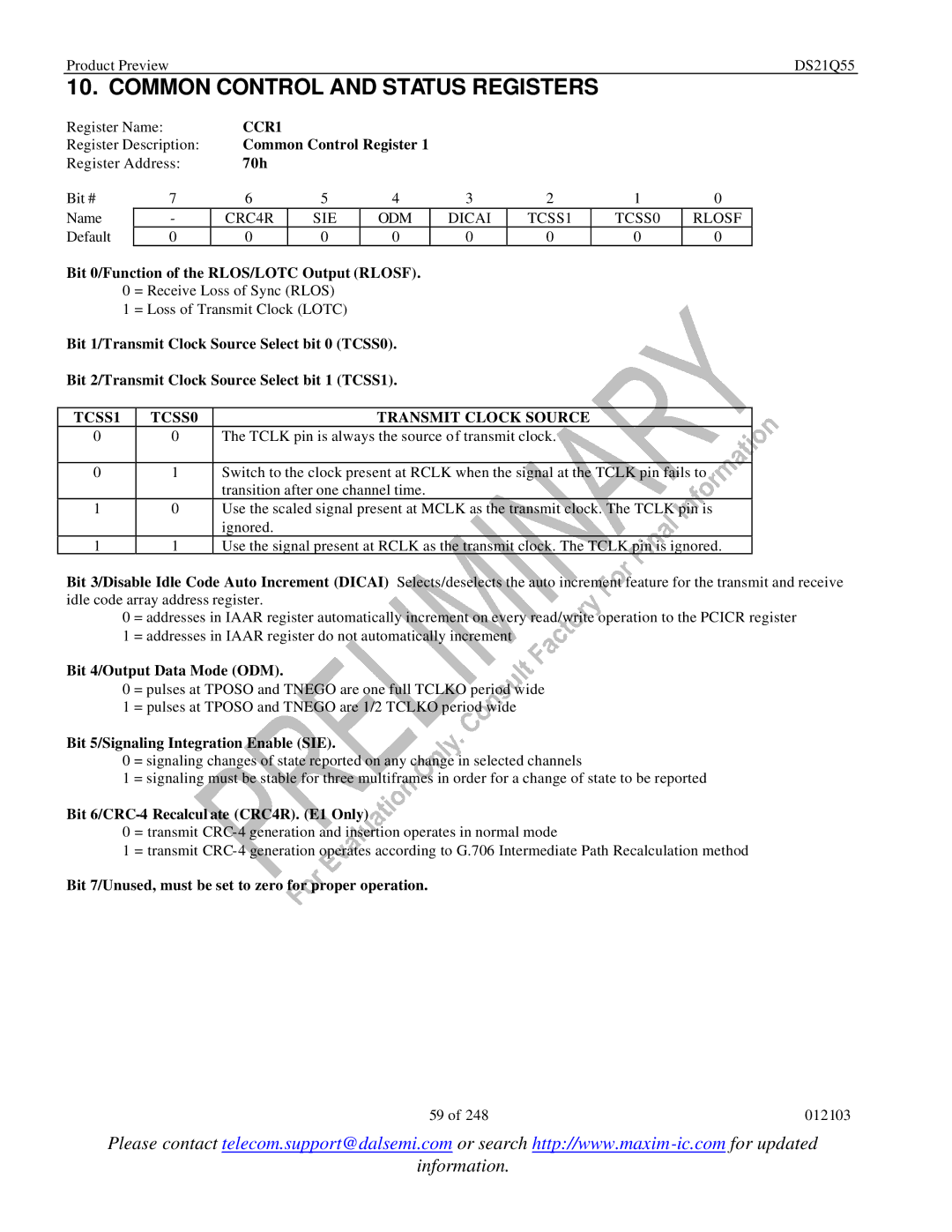

TCSS1 TCSS0 Transmit Clock Source

Common Control and Status Registers

CCR1

SR2

IDR

19h

Bit 2/Receive Unframed All Ones Blue Alarm Condition RUA1

IMR2

Interrupt Mask Register

Lspare LDN LUP Lotc Lorc V52LNK Rdma RRA

SR3

1Ah

Bit 2/V5.2 Link Detected Condition V52LNK

Bit 0/Receive Remote Alarm Condition RRA = interrupt masked

IMR3

1Bh

Bit 2/Receive Multiframe Event RMF

SR4

1Ch

RSA1 RSA0 TMF TAF RMF Rcmf RAF

IMR4

IOCR1

11. I/O PIN Configuration Options

IOCR2

4Ah

Loopback Configuration

Lbcr

Loopback Control Register

Information

PCLR2

Per-Channel Loopback

PCLR1

4Eh

PCLR3

4Dh

PCLR4

Ercnt

Error Count Registers

T1 Operation

Line Code Violation Count Register Lcvcr

T1 Line Code Violation Counting Options Table

E1 Line Code Violation Counting Options Table

LCVCR2

LCVCR1

Line Code Violation Count Register

42h

T1 Path Code Violation Counting Arrangements Table

Framing Mode

Path Code Violation Count Register Pcvcr

ERCNT.1

Framing Mode Count MOS or F-BIT Errors What is Counted

Frames Out Of Sync Count Register Foscr

T1 Frames OUT of Sync Counting Arrangements Table

Information

EBCR1

Bit Counter Register Ebcr

FOSCR1

FOSCR2

TDS0M

14. DS0 Monitoring Function

Transmit DS0 Monitor Registers

TDS0SEL

RDS0M

Receive DS0 Monitor Registers

RDS0SEL

Signaling Operation

Change Of State

Processor-Based Receive Signaling

Hardware-Based Receive Signaling

Receive-Signaling Reinsertion at Rser

Sigcr

Force Receive Signaling All Ones

Receive-Signaling Freeze

Signaling Control Register

CH4-A CH4-B

MSB LSB

MSB LSB CH2-A CH2-B

CH1-A CH1-B

CH9-A CH9-B CH9-C CH9-D RS6

Receive Signaling Registers E1 Mode, CAS Format

RS1 to RS16

60h to 6Fh

RSCSE3

RSCSE1 , RSCSE2 , RSCSE3 , RSCSE4

RSCSE1

RSCSE2

Processor-Based Transmit Signaling

Channel Phone

15.2.1.1 T1 Mode

15.2.1.2 E1 Mode

Time Slot Numbering Schemes Table

TS1 TS2 TS3 TS4 TS5 TS6 TS7 TS8 TS9

Transmit Signaling Registers E1 Mode, CAS Format

TS1 to TS16

50h to 5Fh

Transmit Signaling Registers E1 Mode, CCS Format

50h to 5Bh

Transmit Signaling Registers T1 Mode, ESF Format

TS4

TS1 CH4-A CH4-B

TS2 CH6-A CH6-B

TS3 CH8-A CH8-B

SSIE2

Software Signaling Insertion Enable Registers, E1 CAS Mode

SSIE1

SSIE4

SSIE3

0Ah

Lcaw

Software Signaling Insertion Enable Registers, T1 Mode

Hardware-Based Transmit Signaling

Bits 0-5 of Iaar Register Maps to Channel

PER-CHANNEL Idle Code Generation

Idle Code Array Address Mapping Table

Write Iaar = 40h Write Pcicr = 7Eh

Idle Code Programming Examples

TCICE2

Iaar

Pcicr

TCICE1

Information

RCICE2

TCICE3

TCICE4

RCICE1

87h

RCICE3

86h

RCICE4

RCBR2

Channel Blocking Registers

RCBR1

TCBR2

RCBR3

RCBR4

TCBR1

8Fh

TCBR3

8Eh

TCBR4

Elastic Stores Operation

4Fh

Bit 0/Receive Elastic Store Enable Rese

Escr

Elastic Store Control Register

IMR5

SR5

1Eh

Tesf Tesem Tslip Resf Resem Rslip

Product Preview DS21Q55 109 012103

Receive Side

18.1.1 T1 Mode

18.1.2 E1 Mode

Elastic Stores Initialization

Elastic Store Delay After Initialization Table

Minimum-Delay Mode

Transmit Side

112 012103

CRC-4 Recalculate Method Figure

19. G.706 INT Ermediate CRC-4 Updating E1 Mode only

Receive BOC

20. T1 BIT Oriented Code BOC Controller

Transmit BOC

Rboce RBR RBF1 RBF0 Sboc

Bocc

BOC Control Register

37h

24h

Receive FDL Register

C0h

SR8

IMR8

Internal Register Scheme Based On Double-Frame Method

Additional Sa and International Si BIT Operation E1 only

Hardware Scheme Method

Rnaf

RAF

Tnaf

TAF

C8h

Internal Register Scheme Based On CRC4 Multiframe Method

RSiAF

Receive Si Bits of the Align Frame

RRA

RSa5

RSa4

Receive Sa4 Bits

CBh

RSa7

RSa6

Receive Sa6 Bits

CDh

CFh

RSa8

Receive Sa8 Bits

D2h

TSiAF

Transmit Si Bits of the Align Frame

TRA

TSa5

TSa4

Transmit Sa4 Bits

D5h

TSa7

TSa6

Transmit Sa6 Bits

D7h

D9h

TSa8

Transmit Sa8 Bits

Tsacr

Basic Operation Details

Hdlc Controllers

Hdlc Controller Registers Table

90h, A0h

Hdlc Configuration

H1TC, H2TC

Hdlc #1 Transmit Control, Hdlc #2 Transmit Control

31h, 32h

Bit 0/Receive SS7 Fill In Signal Unit Delete Rsfd

H1RC, H2RC

Hdlc #1 Receive Control, Hdlc #2 Receive Control

TFLWM2 TFLWM1 TFLWM0 Transmit Fifo Watermark Bytes

Fifo Control

H1FC, H2FC

RFHWM2 RFHWM1 RFHWM0 Receive Fifo Watermark Bytes

H2RCS1, H2RCS2, H2RCS3, H2RCS4

Hdlc Mapping

Receive

Register Channels

RCB8SE RCB7SE RCB6SE RCB5SE RCB4SE RCB3SE RCB2SE RCB1SE

H1RTSBS, H2RTSBS

96h, A6h

THCS7 THCS6 THCS5 THCS4 THCS3 THCS2 THCS1 THCS0

Transmit

97h, 98h, 99h, 9Ah A7h, A8h, A9h, AAh

TCB8SE TCB7SE TCB6SE TCB5SE TCB4SE TCB3SE TCB2SE TCB1SE

H1TTSBS, H2TTSBS

9Bh, Abh

Tmend RPE RPS Rhwm RNE Tlwm TNF

SR6, SR7

Hdlc #1 Status Register Hdlc #2 Status Register

20h, 22h

IMR6, IMR7

INFO4

INFO5, INFO6

PS2 PS1 PS0 Packet Status

H1RPBA, H2RPBA

Fifo Information

Receive Packet Bytes Available

H1TFBA, H2TFBA

H1RF, H2RF

22.3.5

H1TF, H2TF

Receive Section

Legacy FDL Support T1 Mode

Receive Hdlc Code Example

RFDLM1, RFDLM2

Rfdl

RFDL7 RFDL6 RFDL5 RFDL4 RFDL3 RFDL2 RFDL1 RFDL0

Transmit FDL Register

22.6 D4/SLC-96 Operation

Transmit Section

Tfdl

Basic Network Connections Figure

Line Interface Unit LIU

LIU Receiver

LIU Operation

Typical Monitor Application Figure

Receive G.703 Synchronization Signal E1 Mode

Monitor Mode

Transmit Short-Circuit Detector/Limiter

Transmit BPV Error Insertion

Transmit G.703 Synchronization Signal E1 Mode

LIU Transmitter

CMI Coding Figure

Mclk Prescaler

CMI Code Mark Inversion Option

LIC1

23.7 LIU Control Registers

Application Return Loss

E1 Mode

7Dh

Network Mode GC5 GC4 GC3 GC2 GC1 GC0

Tlbc

Transmit Line Build-Out Control

Bit 7/E1/T1 Select ETS

LIC2

79h

ETS Lirst Ibpv TUA1 Jamux Scld Clds

MM1 MM0

LIC3

MPS1 MPS0 Jamux LIC2.3

RT1 RT0 Internal Receive Termination Configuration

TT1 TT0 Internal Transmit Termination Configuration

LIC4

RL3 RL2 RL1 RL0

INFO2

CCR4

Lrcl Tcle Tocd Lolitc

Ilut Timer Rscos

SR1

16h

17h

Timer Rscos

IMR1

1µF

Recommended Circuits Basic Interface Figure

Protected Interface Using Internal Receive Termination

Specification Recommended Value

Component Specifications Transformer Specifications Table

T1 Transmit Pulse Template Figure

E1 Transmit Pulse Template Figure

Jitter Tolerance E1 Mode Figure

Jitter Tolerance T1 Mode Figure

Jitter Attenuation E1 Mode Figure

Jitter Attenuation T1 Mode Figure

Programmable IN-BAND Loop Code Generation and Detection

TC1 TC0

Ibcc

RDN2 RDN1 RDN0

RUP2 RUP1 RUP0

TCD2

TCD1

Transmit Code Definition Register

B7h

RUPCD2

RUPCD1

RDNCD1

RSC2 RSC1 RSC0

RDNCD2

Rscc

RSCD2

RSCD1

Receive -Spare Code Definition Register

BEh

Bert Function

PS2 PS1 PS0 Pattern Definition

Bert Register Description

BC1

Length Bits

EIB2 EIB1 EIB0 Error Rate Inserted

BC2

E1h

EAh

Bit 0/BERT Enable Berten = Bert disabled

BIC

BER T Interface Control Register

Bbed Bbco BEC0 BRA1 BRA0 Brlos Bsync

SR9

26h

Bawc

IMR9

BRP3

Bert Repetitive Pattern Set

BRP1

BRP2

BBC3

Bert Bit Counter

BBC1

BBC2

BEC3

Bert Error Counter

BEC1

BEC2

Step Action

Payload Error Insertion Function

Transmit Error Insertion Setup Sequence Table

ERC

Error Rate Control Register

Bits 0 to 3/Error Insertion Rate Select Bits ER0 to ER3

ER3 ER2 ER1 ER0 Error Rate

NOE1

Number Of Error Registers

Error Insertion Examples Table

Value Write Read

NOEL2

Number Of Errors Left Register

NOEL1

Interleaved PCM BUS Operation

Channel Interleave Mode

Frame Interleave Mode

IBS1 IBS0 BUS Size

Iboc

DA0 Device Position

DS21Q55 #1 Rser DS21Q55 #3 Rser

IBO Example Figure

Esib Group of Four DS21Q55s Figure

Extended System Information BUS Esib

ESIBSEL2 ESIBSEL1 ESIBSEL0 BUS BIT Driven

ESIBCR1

Extended System Information Bus Control Register

B0h

B1h

ESI3SEL2 ESI3SEL1 ESI3SEL0 Status Output T1 Mode E1 Mode

ESI4SEL2 ESI4SEL1 ESI4SEL0 Status Output T1 Mode E1 Mode

ESIBCR2

ESIB4

ESIB1

ESIB2

ESIB3

BPCS1 BPCS0

Programmable Backplane Clock Synthesizer

CCR2

Tdatfmt Tgpcken Rdatfmt Rgpcken

Fractional T1/E1 Support

CCR3

72h

Jtag Functional Block Diagram Figure

JTAG-BOUNDARY-SCAN Architecture and TEST-ACCESS Port

Run-Test-Idle

Test-Logic-Reset

Update-DR

TAP Controller State Machine

Shift-IR

Update-IR

Select-IR-Scan

Capture-IR

TAP Controller State Diagram Figure

Instruction Selected Register Instruction Codes

Instruction Register

Instruction Codes for Ieee 1149.1 Architecture Table

Device BIT ID

ID Code Structure Table

Device ID Codes Table

MSB LSB

Identification Register

Test Registers

Boundary Scan Register

Bypass Register

ESIBS0

BIT PIN Symbol Type Control BIT Description

Boundary Scan Control Bits Table

Rchblk Jtms Bpclk Jtclk Jtrst

Esibrd

Tsig Teso NXA Tdata NXA Tsysclk Tssync Tchclk

ESIBS1 MUX

Dvss Dvdd

Rsysclk

Rsync RLOS/LOTC

Receive Side ESF Timing Figure

Rclk

Rsysclk

Rsysclk Rser

Transmit Side D4 Timing Figure

Transmit Side ESF Timing Figure

Transmit Side Boundary Timing With Elastic Store Disabled

Tsysclk

TSER1

32.2 E1 Mode Receive Side Timing Figure

Receive Side Boundary Timing With Elastic Store Disabled

RSYNC2 Rmsync RSYNC3 Rchclk Rchblk

221 012103

Receive IBO Channel Interleave Mode Timing Figure

Receive IBO Frame Interleave Mode Timing Figure

TIMING, E1 Mode only Figure

Transmit Side Timing Figure

Tser LSB Si

Tssync Tchclk Tchblk

228 012103

Transmit IBO Channel Interleave Mode Timing Figure

Transmit IBO Frame Interleave Mode Timing Figure

THETA-JA θJA vs Airflow

Thermal Characteristics

Operating Parameters Absolute Maximum Ratings

Capacitance

DC Characteristics

Parameter Symbol MIN TYP MAX

Recommended DC Operating Conditions

Parameter Symbol MIN TYP MAX Units

AC Timing Parameters and Diagrams

Intel BUS Write Timing BTS = 0 / MUX = 1 Figure

Intel BUS Read Timing BTS = 0 / MUX = 1 Figure

Motorola BUS Timing BTS = 1 / MUX = 1 Figure

236 012103

Intel BUS Read Timing BTS = 0 / MUX = 0 Figure

Motorola BUS Read Timing BTS = 1 / MUX = 0 Figure

Parameter Symbol MIN TYP MAX Units

Receive Side AC Characteristics

AC CHARACTERISTICS-RECEIVE Side

Receive Side Timing T1 Mode Figure

Receive Side TIMING, Elastic Store Enabled T1 Mode Figure

Receive Line Interface Timing Figure

MAX Units

Transmit AC Characteristics

Parameter Symbol MIN

TYP E1

Tsysclk = 8.192MHz Tsysclk = 16.384MHz

Transmit Side TIMING, Elastic Store Enabled Figure

Transmit Line Interface Timing Figure

Mechanical Descriptions

Product Preview DS21Q55 248 012103

![]()

![]() 0 = pulses at TPOSO and TNEGO are one full TCLKO period wide 1 = pulses at TPOSO and TNEGO are 1/2 TCLKO period wide

0 = pulses at TPOSO and TNEGO are one full TCLKO period wide 1 = pulses at TPOSO and TNEGO are 1/2 TCLKO period wide