Canopy T1/E1 Multiplexer | September 2004 | |

| T1/E1 Multiplexer FPGA Version 3.4 | |

|

|

|

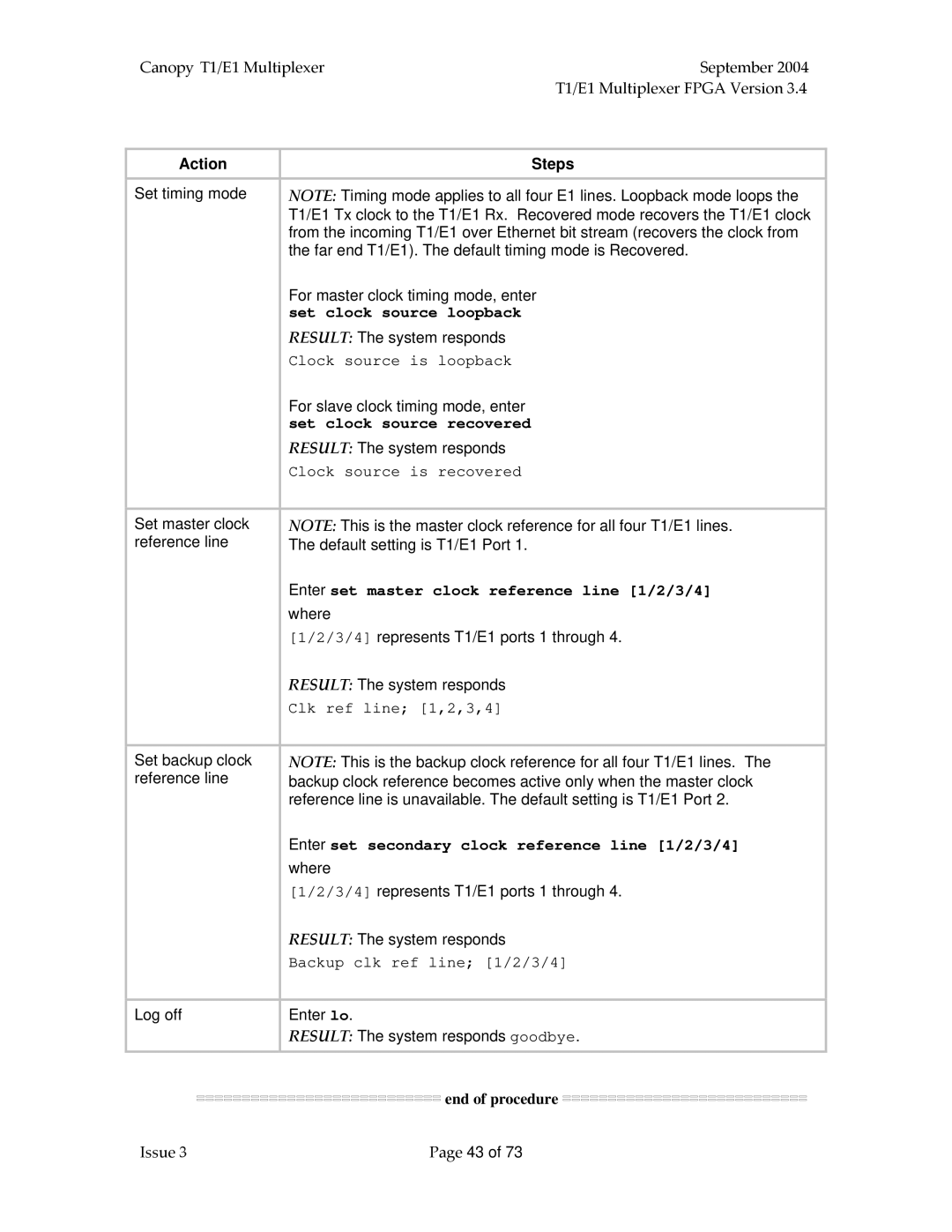

Action | Steps |

|

|

| |

Set timing mode | NOTE: Timing mode applies to all four E1 lines. Loopback mode loops the | |

| T1/E1 Tx clock to the T1/E1 Rx. Recovered mode recovers the T1/E1 clock | |

| from the incoming T1/E1 over Ethernet bit stream (recovers the clock from | |

| the far end T1/E1). The default timing mode is Recovered. |

|

| For master clock timing mode, enter |

|

| set clock source loopback |

|

| RESULT: The system responds |

|

| Clock source is loopback |

|

| For slave clock timing mode, enter |

|

| set clock source recovered |

|

| RESULT: The system responds |

|

| Clock source is recovered |

|

|

| |

Set master clock | NOTE: This is the master clock reference for all four T1/E1 lines. | |

reference line | The default setting is T1/E1 Port 1. |

|

| Enter set master clock reference line [1/2/3/4] | |

| where |

|

| [1/2/3/4] represents T1/E1 ports 1 through 4. |

|

| RESULT: The system responds |

|

| Clk ref line; [1,2,3,4] |

|

|

| |

Set backup clock | NOTE: This is the backup clock reference for all four T1/E1 lines. The | |

reference line | backup clock reference becomes active only when the master clock | |

| reference line is unavailable. The default setting is T1/E1 Port 2. | |

| Enter set secondary clock reference line [1/2/3/4] | |

| where |

|

| [1/2/3/4] represents T1/E1 ports 1 through 4. |

|

| RESULT: The system responds |

|

| Backup clk ref line; [1/2/3/4] |

|

|

|

|

Log off | Enter lo. |

|

| RESULT: The system responds goodbye. |

|

end of procedure

end of procedure

Issue 3 | Page 43 of 73 |