Data Manual

ROM

Gpio MUX

ROM Timing C280x only

Typical Operational Power Versus Frequency F2808

Warm Reset

TMS320F2809, TMS320F2808, TMS320F2806

Xclkin Timing Requirements PLL Enabled

Features

Check for

Getting Started

Acquire the appropriate development tools

Download starter software

Download flash programming software

Introduction

Hardware Features 100-MHz Devices

Feature TYPE1

Hardware Features 60-MHz Devices

Feature

Pin Assignments

TMS320F2809, TMS320F2808 100-Pin PZ Lqfp Top View

TMS320F2806 100-Pin PZ Lqfp Top View

On the C280x devices, the VDD3VFL pin is Vddio

TMS320F2801x 100-Pin PZ Lqfp Top View

Bottom View

Signal Descriptions

Signal Descriptions

ADC Signals

Reset

CPU and I/O Power Pins

Gpioa and Peripheral Signals 2

Signal Descriptions

TMS320F2809, TMS320F2808, TMS320F2806

TMS320C2801, TMS320F28016, TMS320F28015

GPIO33

Functional Block Diagram

Protected by the CODE-SECURITY Module

Memory Maps

F2809 Memory Map

F2808 Memory Map

F2806 Memory Map

F2802, C2802 Memory Map

F2801, F28015, F28016, C2801 Memory Map

Addresses of Flash Sectors in F2809

Addresses of Flash Sectors in F2808

Addresses of Flash Sectors in F2806, F2802

Address Range Program and Data Space

Addresses of Flash Sectors in F2801, F28015, F28016

Impact of Using the Code Security Module

Address Flash ROM

Wait-states

Area WAIT-STATES Comments

OTP

H0 Saram

Brief Descriptions

1 C28x CPU

Memory Bus Harvard Bus Architecture

Peripheral Bus

Real-Time Jtag and Analysis

Flash

6 ROM

7 M0, M1 SARAMs

Boot Mode Selection

Boot ROM

8 L0, L1, H0 SARAMs

Security

Disclaimer Code Security Module Disclaimer

Low-Power Modes

Peripheral Interrupt Expansion PIE Block

External Interrupts XINT1, XINT2, Xnmi

Oscillator and PLL

19 32-Bit CPU-Timers 0, 1

Peripheral Frames 0, 1, 2 PFn

General-Purpose Input/Output Gpio Multiplexer

Control Peripherals

Serial Port Peripherals

Register Map

Access Type

Peripheral Frame 0 Registers1

Peripheral Frame 1 Registers1

Name Address Range

Device Emulation Registers

Interrupts

10. Peripheral Frame 2 Registers1

11. Device Emulation Registers

External and PIE Interrupt Sources

MUX

INT1 INT2 INT11 INT12

Intm

External Interrupts

13. PIE Configuration and Control Registers

14. External Interrupt Registers

System Control

15. PLL, Clocking, Watchdog, and Low-Power Mode Registers1

OSC and PLL Block

External Clock Signal Toggling 0 −V DD

Crystal

17. Possible PLL Configuration Modes

PLL Mode Remarks Pllstsclkindiv Sysclkout Clkin

PLL-Based Clock Module

16. Pllcr Register Bit Definitions

Loss of Input Clock

Watchdog Block

Low-Power Modes Block

18. Low-Power Modes

LPMCR010

Oscclk Clkin Sysclkout

32-Bit CPU-Timers 0/1/2

Tddrhtddr

Prdhprd

Pschpsc TCR.4

CPU-Timers 0, 1, 2 Configuration and Control Registers

Enhanced PWM Modules ePWM1/2/3/4/5/6

EPWM1 EPWM2 EPWM3 EPWM4 EPWM5 EPWM6 Size

EPWM Control and Status Registers

#SHADOW

CTR = Zero

Hi-Resolution PWM Hrpwm

Enhanced CAP Modules eCAP1/2/3/4

Ctrphs

Ctrovf OVF

RST

CTR=PRD CTR=CMP

ECAP1 ECAP2 ECAP3 ECAP4

ECAP Control and Status Registers

Size Description

Enhanced QEP Modules eQEP1/2

EQEP Control and Status Registers

EQEP1 EQEP2

Register Description

Address #SHADOW

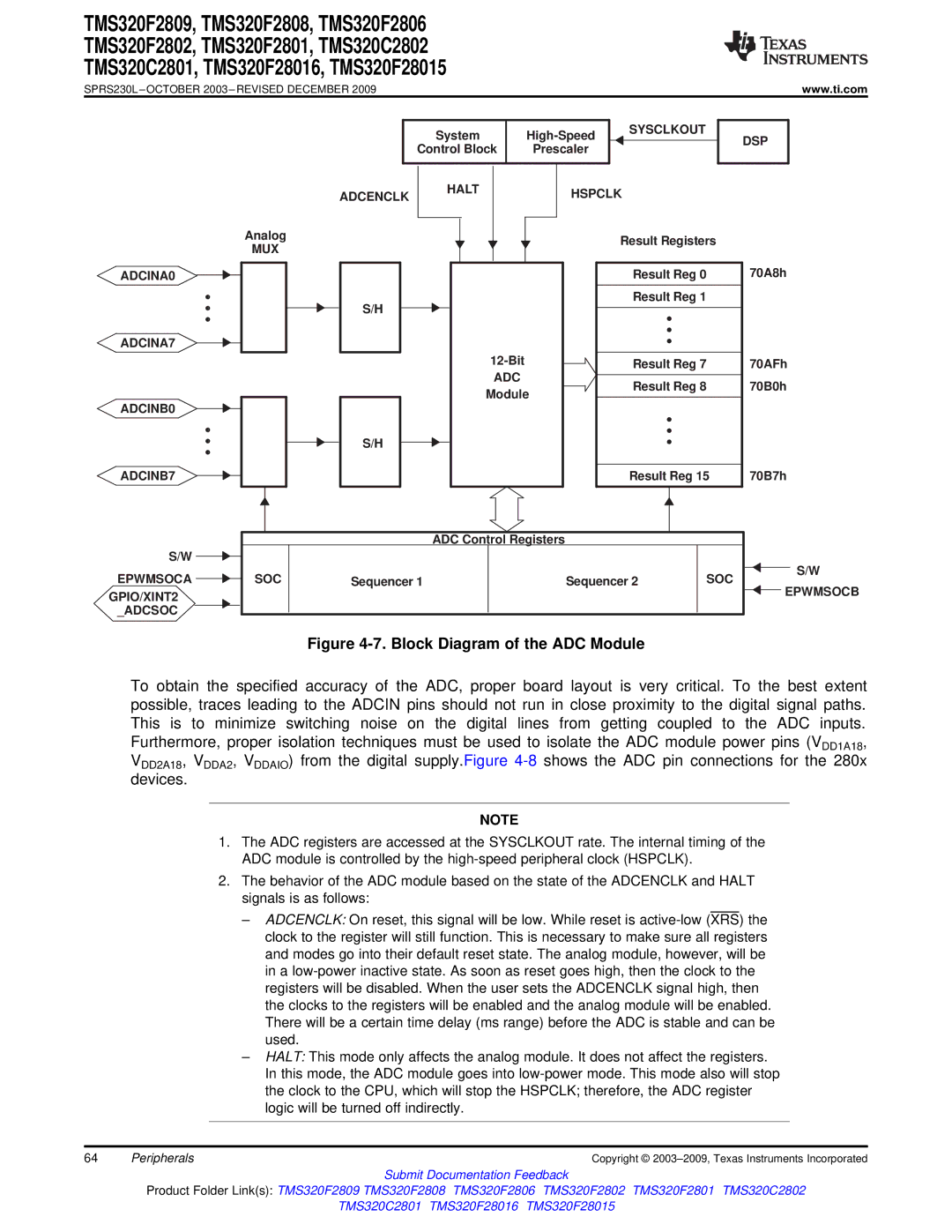

Enhanced Analog-to-Digital Converter ADC Module

Sysclkout DSP Adcenclk Halt Hspclk

ADCINA0

ADCINA7

ADCINB0 ADCINB7

ADCINA70

ADCINB70

Adclo

Adcrefin

ADC Connections if the ADC Is Not Used

Adcresext

ADC Registers

ADC Registers1

Peripherals

TMS320F2809, TMS320F2808, TMS320F2806

TMS320F2802, TMS320F2801, TMS320C2802

SN65HVD23x

Can Bus

11. eCAN-A Memory Map

12. eCAN-B Memory Map

Can Register Map1

Register Name

ECAN-A ECAN-B

Size Description Address

Serial Communications Interface SCI Modules SCI-A, SCI-B

SCI-A Registers1

SCI-B Registers1

13. Serial Communications Interface SCI Module Block Diagram

When Spibrr = 3 to

10. SPI-A Registers

11. SPI-B Registers

12. SPI-C Registers

13. SPI-D Registers

14. SPI Module Block Diagram Slave Mode

−−−−−

Inter-Integrated Circuit I2C

14. I2C-A Registers

Gpio MUX Sdaa Scla

I2CAENCLK I2C−A C28X CPU Sysclkout

Sysrs

Gpiolmpsel GPIOXINT1SEL GPIOXINT2SEL

Gpioxnmisel

Gpio Control Registers Eallow Protected

15. Gpio Registers

Gpio Data Registers not Eallow Protected

16. F2808 Gpio MUX Table

GPAMUX1/2

GPAMUX1

GPAMUX2

Time between samples GPyCTRL Reg GPIOx

Sync Sysclkout

Software Development Tools

Device and Development Support Tool Nomenclature

Hardware Development Tools

Temperature Range

TMS

Prefix

Device Family

Documentation Support

TMS320x280x, 2801x Peripheral Selection Guide

Literature

Peripheral Guide

TMS320C28x

Application Programming Interface API Reference

Application Reports and Software

TMS320x281x to TMS320x2833x or 2823x Migration Overview

TMS320x280x to TMS320x2833x or 2823x Migration Overview

C28x FPU Primer

SPRA820

Software

Device Support

Electrical Specifications

Absolute Maximum Ratings1

Electrical Characteristics

Recommended Operating Conditions

MIN NOM MAX Unit

Parameter Test Conditions MIN TYP MAX Unit

Current Consumption

Sysclkout

TYP5 MAX6

SCI-A SPI-A ADC

TYP4 MAX5

Reducing Current Consumption

Peripheral DD Current Module

ADC I2C

SCI SPI

Total Power

Current Consumption Graphs

IDD IDDA18

Iddio

Typical Operational Power Versus Frequency C280x

Typical Operational Current Versus Frequency C280x

Emulator Connection Without Signal Buffering for the DSP

EMU0 EMU1 Trst TMS TDI TDO TCK DSP GND Tckret Jtagheader

Timing Parameter Symbology

General Notes on Timing Parameters

Test Load Circuit

85 pF

Device Clock Table

TMS320x280x Clock Table and Nomenclature 100-MHz Devices

Clock Requirements and Characteristics

XCLKIN1 Timing Requirements PLL Enabled

10. XCLKIN1 Timing Requirements PLL Disabled

Input Clock Frequency

Power Sequencing

Power Management and Supervisory Circuit Solutions

12. Power Management and Supervisory Circuit Solutions

Xclkina Xclkoutb

Xclkout

OSCCLK/8A

Xclkout XRS

13. Reset XRS Timing Requirements

OSCCLK/8

14. General-Purpose Output Switching Characteristics

General-Purpose Input/Output Gpio

Gpio Output Timing

Sysclkout Oscclk OSCCLK/2

Gpio Signal GPxQSELn = 1,0 6 samples

Gpio Input Timing

Sysclkout Qualprd = 1 SYSCLKOUT/2

Output From Qualifier

Case

Sampling Window Width for Input Signals

GPIOxn

Low-Power Mode Wakeup Timing

16. Idle Mode Timing Requirements1

17. Idle Mode Switching Characteristics1

Address/Data Internal

18. Standby Mode Timing Requirements

19. Standby Mode Switching Characteristics

Test Conditions MIN NOM MAX Unit

Xclkin Xclkout Standby

20. Halt Mode Timing Requirements

21. Halt Mode Switching Characteristics

23. ePWM Switching Characteristics

Enhanced Control Peripherals

Enhanced Pulse Width Modulator ePWM Timing

Trip-Zone Input Timing

27. eCAP Switching Characteristics

29. eQEP Switching Characteristics

26. Enhanced Capture eCAP Timing Requirement1

MIN TYP MAX Unit

32. External Interrupt Switching Characteristics1

External Interrupt Timing

Parameter

Adcsocbo

10.4 I2C Electrical Specification and Timing

Serial Peripheral Interface SPI Master Mode Timing

33. I2C Timing

Vddio

34. SPI Master Mode External Timing Clock Phase = 0 1 2 3 4

Spisomi Master In Data Must Be Valid

Spisimo

Spistea

35. SPI Master Mode External Timing Clock Phase = 1 1 2 3 4

Spiclk

Clock polarity =

Data Valid

Spisomi

SPI Slave Mode Timing

36. SPI Slave Mode External Timing Clock Phase = 01 2 3 4

37. SPI Slave Mode External Timing Clock Phase = 11 2

Spisimo Data Must Be Valid

On-Chip Analog-to-Digital Converter

ADC Power-Up Control Bit Timing

Analog Inputs

Converter

Conversion Modes

ADCIN0

AT 12.5 MHz Sample n Sample n +

Sequential Sampling Mode Single-Channel Smode =

ADC Clock Remarks

Simultaneous Sampling Mode Dual-Channel Smode =

Detailed Descriptions

43. Flash Endurance for a and S Temperature Material1

44. Flash Endurance for Q Temperature Material1

46. Flash/OTP Access Timing

Flash Timing

48. ROM/OTP Access Timing

ROM Timing C280x only

Sysclkout ns

Flash Flash Random OTP WAIT-STATE

Migration Issues

ADDITIONS, DELETIONS, and Modifications

F280x Thermal Model 100-pin GGM Results

F280x Thermal Model 100-pin PZ Results

C280x Thermal Model 100-pin GGM Results

C280x Thermal Model 100-pin PZ Results

F2809 Thermal Model 100-pin PZ Results

ΨJTC/W

Orderable Device

Package Type Pins Package Qty Eco Plan Lead

Samples

Package Qty Eco Plan Lead

TMS320F2802ZGMA Active

TMS320F2802ZGMS Active

TMS320F2806GGMA Active

Microstar TMS320F2806GGMS Active

TMS320F2809ZGMA Active

TMS320F2809ZGMS Active

GGM S-PBGA-N100

10,10 20 TYP

40 MAX

4145257-3/C 12/01

Page

PZ S-PQFP-G100

Plastic Quad Flatpack

DSP

Products Applications

Rfid

EPWMSOCB

EPWMSOCB