6 F 3 B 0 3 6 2

(3)Status (B)

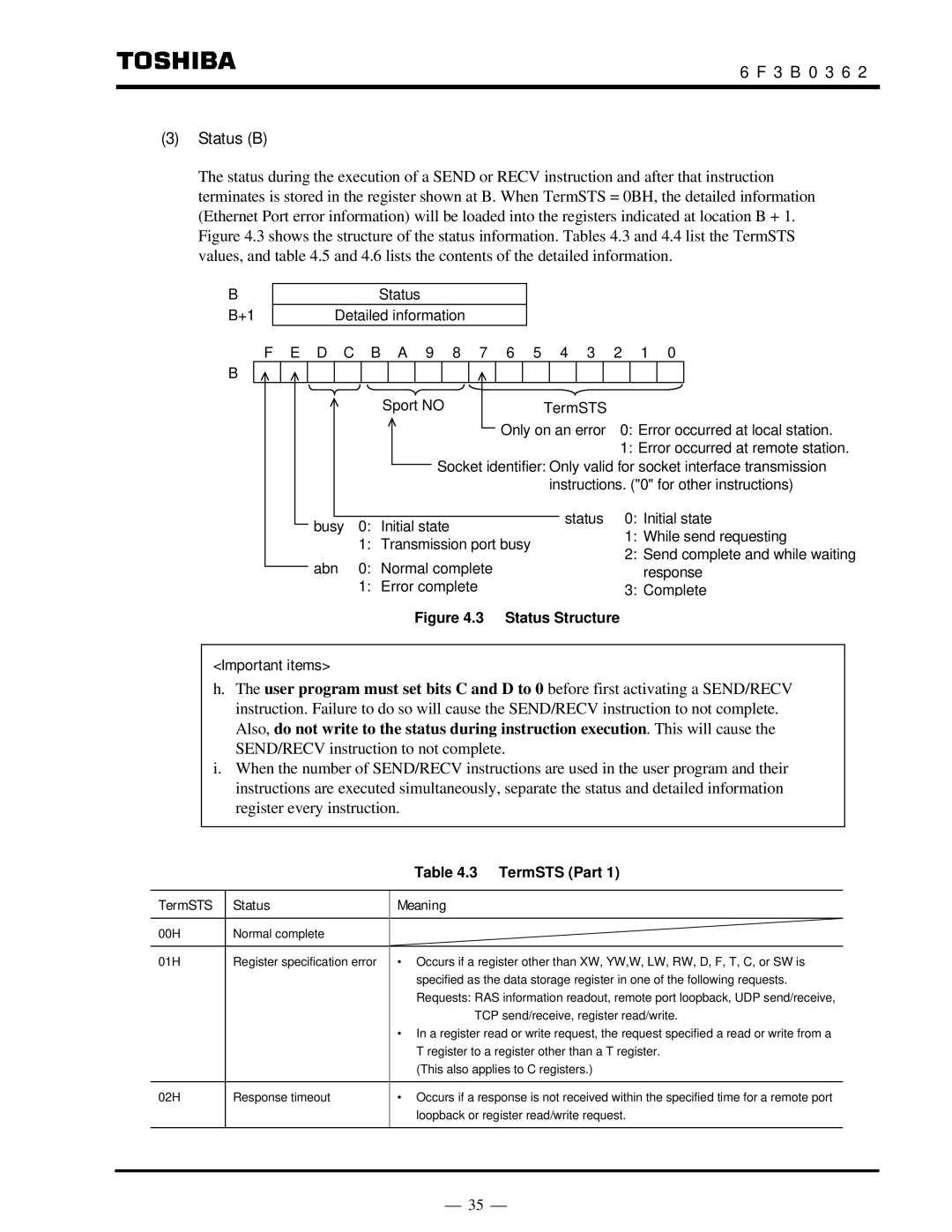

The status during the execution of a SEND or RECV instruction and after that instruction terminates is stored in the register shown at B. When TermSTS = 0BH, the detailed information (Ethernet Port error information) will be loaded into the registers indicated at location B + 1. Figure 4.3 shows the structure of the status information. Tables 4.3 and 4.4 list the TermSTS values, and table 4.5 and 4.6 lists the contents of the detailed information.

B B+1

Status

Detailed information

F E D C B A 9 8 7 6 5 4 3 2 1 0

B |

|

|

|

| Sport NO | TermSTS |

|

|

| Only on an error | 0: Error occurred at local station. |

|

|

| 1: Error occurred at remote station. |

| Socket identifier: Only valid for socket interface transmission | ||

|

| instructions. ("0" for other instructions) | |

busy | 0: Initial state | status | 0: Initial state |

| 1: While send requesting | ||

| 1: Transmission port busy | ||

| 2: Send complete and while waiting | ||

abn | 0: Normal complete |

| |

| response | ||

| 1: Error complete |

| 3: Complete |

| Figure 4.3 | Status Structure |

|

<Important items>

h.The user program must set bits C and D to 0 before first activating a SEND/RECV instruction. Failure to do so will cause the SEND/RECV instruction to not complete. Also, do not write to the status during instruction execution. This will cause the SEND/RECV instruction to not complete.

i.When the number of SEND/RECV instructions are used in the user program and their instructions are executed simultaneously, separate the status and detailed information register every instruction.

Table 4.3 TermSTS (Part 1)

TermSTS | Status |

|

|

00H | Normal complete |

|

|

01H | Register specification error |

02H | Response timeout |

Meaning

•Occurs if a register other than XW, YW,W, LW, RW, D, F, T, C, or SW is specified as the data storage register in one of the following requests. Requests: RAS information readout, remote port loopback, UDP send/receive,

TCP send/receive, register read/write.

•In a register read or write request, the request specified a read or write from a T register to a register other than a T register.

(This also applies to C registers.)

•Occurs if a response is not received within the specified time for a remote port loopback or register read/write request.

⎯ 35 ⎯