IXP1200 Network Processor Family ATM

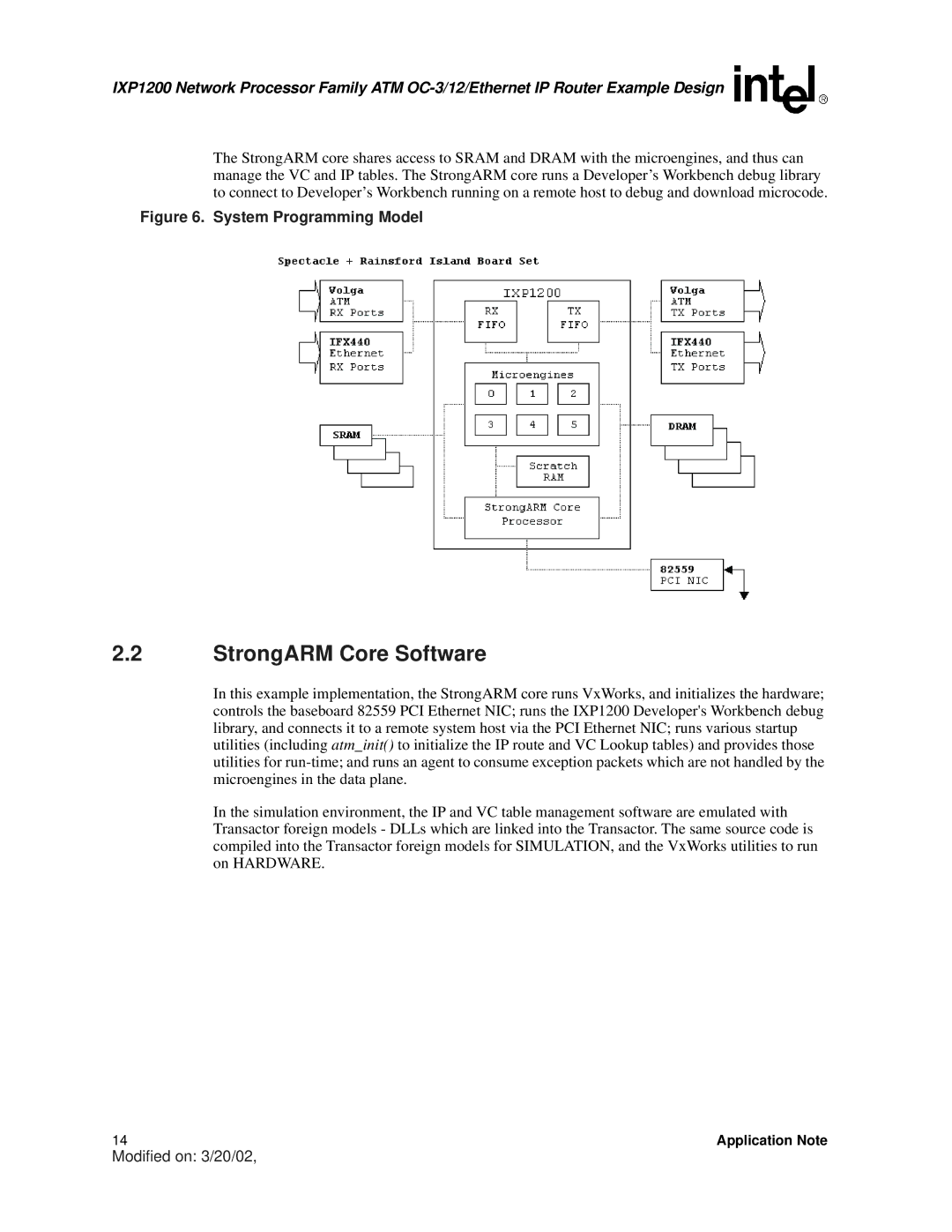

The StrongARM core shares access to SRAM and DRAM with the microengines, and thus can manage the VC and IP tables. The StrongARM core runs a Developer’s Workbench debug library to connect to Developer’s Workbench running on a remote host to debug and download microcode.

Figure 6. System Programming Model

2.2StrongARM Core Software

In this example implementation, the StrongARM core runs VxWorks, and initializes the hardware; controls the baseboard 82559 PCI Ethernet NIC; runs the IXP1200 Developer's Workbench debug library, and connects it to a remote system host via the PCI Ethernet NIC; runs various startup utilities (including atm_init() to initialize the IP route and VC Lookup tables) and provides those utilities for

In the simulation environment, the IP and VC table management software are emulated with Transactor foreign models - DLLs which are linked into the Transactor. The same source code is compiled into the Transactor foreign models for SIMULATION, and the VxWorks utilities to run on HARDWARE.

14 | Application Note |

Modified on: 3/20/02,