IXP1200 Network Processor Family ATM

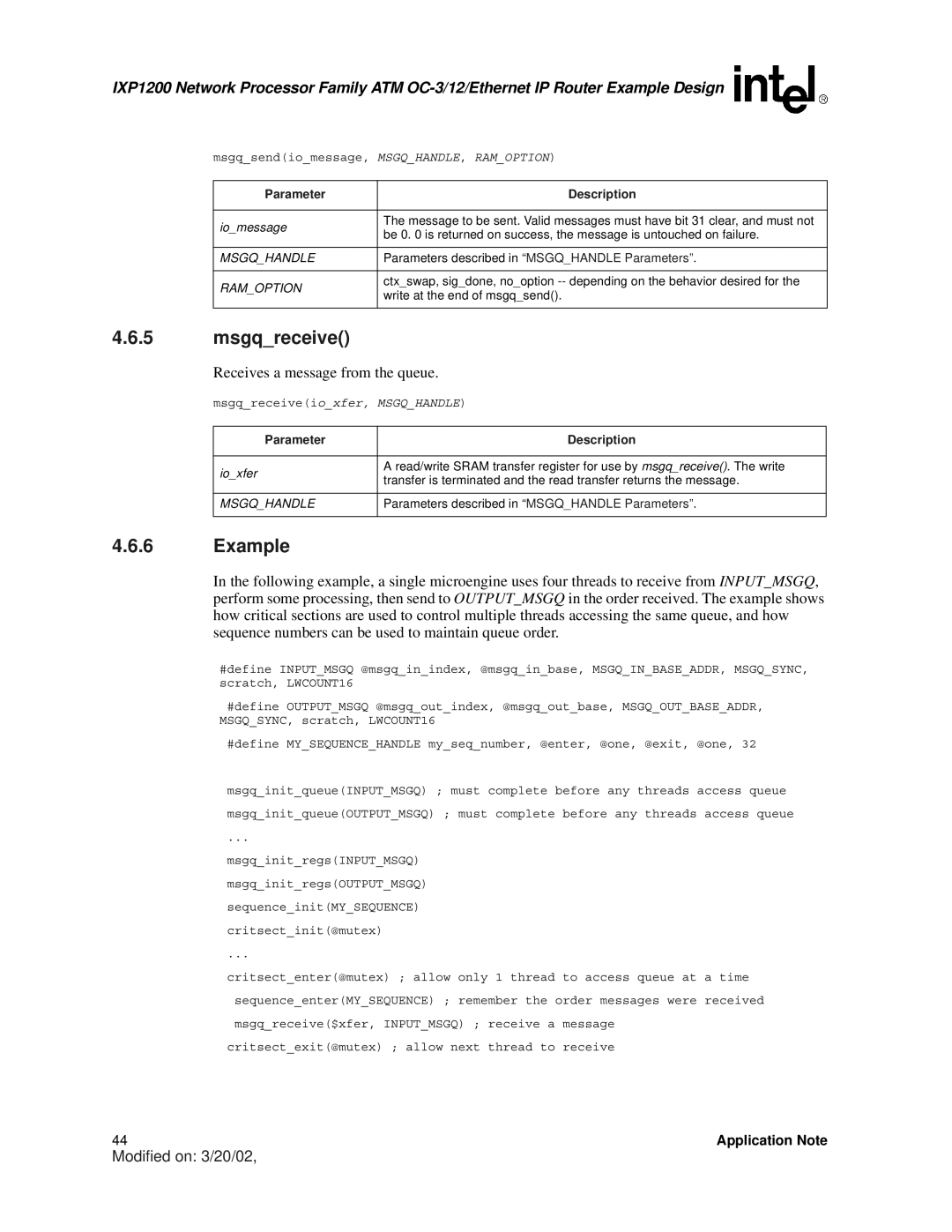

msgq_send(io_message, MSGQ_HANDLE, RAM_OPTION)

Parameter | Description | |

|

| |

io_message | The message to be sent. Valid messages must have bit 31 clear, and must not | |

be 0. 0 is returned on success, the message is untouched on failure. | ||

| ||

|

| |

MSGQ_HANDLE | Parameters described in “MSGQ_HANDLE Parameters”. | |

|

| |

RAM_OPTION | ctx_swap, sig_done, no_option | |

write at the end of msgq_send(). | ||

| ||

|

|

4.6.5msgq_receive()

Receives a message from the queue.

msgq_receive(io_xfer, MSGQ_HANDLE)

Parameter | Description | |

|

| |

io_xfer | A read/write SRAM transfer register for use by msgq_receive(). The write | |

transfer is terminated and the read transfer returns the message. | ||

| ||

|

| |

MSGQ_HANDLE | Parameters described in “MSGQ_HANDLE Parameters”. | |

|

|

4.6.6Example

In the following example, a single microengine uses four threads to receive from INPUT_MSGQ, perform some processing, then send to OUTPUT_MSGQ in the order received. The example shows how critical sections are used to control multiple threads accessing the same queue, and how sequence numbers can be used to maintain queue order.

#define INPUT_MSGQ @msgq_in_index, @msgq_in_base, MSGQ_IN_BASE_ADDR, MSGQ_SYNC, scratch, LWCOUNT16

#define OUTPUT_MSGQ @msgq_out_index, @msgq_out_base, MSGQ_OUT_BASE_ADDR, MSGQ_SYNC, scratch, LWCOUNT16

#define MY_SEQUENCE_HANDLE my_seq_number, @enter, @one, @exit, @one, 32

msgq_init_queue(INPUT_MSGQ) ; must complete before any threads access queue msgq_init_queue(OUTPUT_MSGQ) ; must complete before any threads access queue

...

msgq_init_regs(INPUT_MSGQ) msgq_init_regs(OUTPUT_MSGQ) sequence_init(MY_SEQUENCE) critsect_init(@mutex)

...

critsect_enter(@mutex) ; allow only 1 thread to access queue at a time sequence_enter(MY_SEQUENCE) ; remember the order messages were received msgq_receive($xfer, INPUT_MSGQ) ; receive a message

critsect_exit(@mutex) ; allow next thread to receive

44 | Application Note |

Modified on: 3/20/02,