IXP1200 Network Processor Family ATM

2.4.2Ethernet to ATM Data Flow

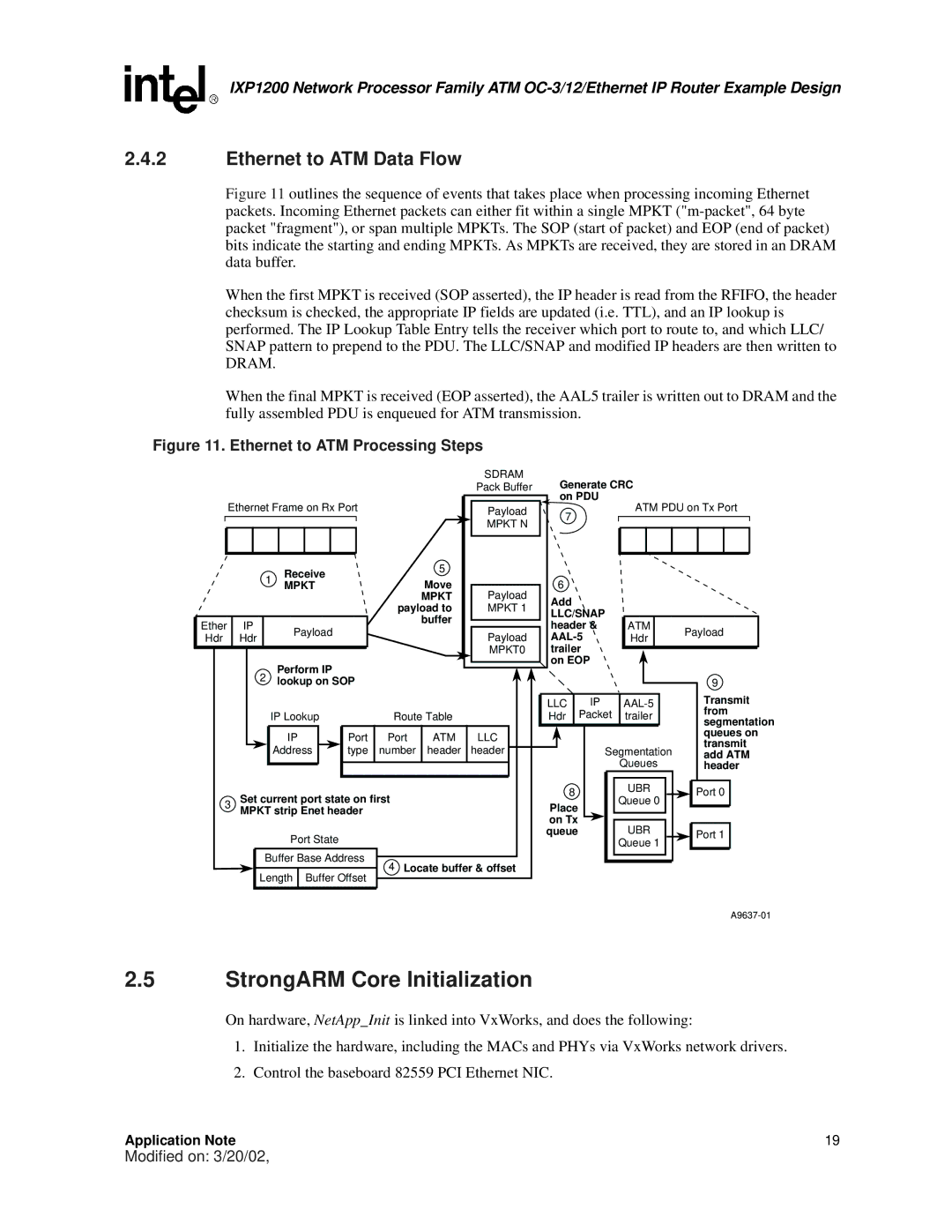

Figure 11 outlines the sequence of events that takes place when processing incoming Ethernet packets. Incoming Ethernet packets can either fit within a single MPKT ("m-packet", 64 byte packet "fragment"), or span multiple MPKTs. The SOP (start of packet) and EOP (end of packet) bits indicate the starting and ending MPKTs. As MPKTs are received, they are stored in an DRAM data buffer.

When the first MPKT is received (SOP asserted), the IP header is read from the RFIFO, the header checksum is checked, the appropriate IP fields are updated (i.e. TTL), and an IP lookup is performed. The IP Lookup Table Entry tells the receiver which port to route to, and which LLC/ SNAP pattern to prepend to the PDU. The LLC/SNAP and modified IP headers are then written to DRAM.

When the final MPKT is received (EOP asserted), the AAL5 trailer is written out to DRAM and the fully assembled PDU is enqueued for ATM transmission.

Figure 11. Ethernet to ATM Processing Steps

SDRAM

Pack Buffer Generate CRC on PDU

| Ethernet Frame on Rx Port | Payload | 7 | ATM PDU on Tx Port | |||||||||

|

|

|

|

|

|

| MPKT N |

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 1 | Receive |

|

| 5 |

|

|

|

|

| |

|

|

| Move |

| 6 |

|

|

| |||

| MPKT |

|

|

|

|

|

| ||||

|

|

|

|

| Payload |

|

|

| |||

|

|

|

|

|

| MPKT | Add |

|

|

| |

|

|

|

|

| payload to | MPKT 1 |

|

|

| ||

|

|

|

|

| LLC/SNAP |

|

| ||||

|

|

|

|

|

| buffer |

|

|

| ||

Ether | IP |

|

|

|

|

| header & | ATM |

| ||

| Payload |

|

|

|

| Payload | |||||

Hdr | Hdr |

|

|

|

| Payload | Hdr | ||||

|

|

|

|

|

| ||||||

|

|

|

|

|

|

| MPKT0 | trailer |

|

| |

|

|

| Perform IP |

|

|

|

| on EOP |

|

| |

| 2 |

|

|

|

|

|

|

|

|

| |

|

| lookup on SOP |

|

|

|

|

|

| 9 | ||

|

|

|

|

|

|

|

| LLC | IP | Transmit | |

|

| IP Lookup |

| Route Table |

| Hdr | Packet | trailer | from | ||

|

|

|

| segmentation | |||||||

|

|

|

|

|

|

|

|

|

|

| |

|

|

| IP | Port | Port | ATM | LLC |

|

|

| queues on |

|

|

|

|

|

| transmit | |||||

|

|

| Address | type | number | header | header |

| Segmentation | ||

|

|

|

| add ATM | |||||||

|

|

|

|

|

|

|

|

|

| Queues | header |

| Set current port state on first |

|

| 8 |

| UBR | Port 0 | ||||

|

|

|

| Queue 0 | |||||||

3 |

|

| Place |

|

| ||||||

MPKT strip Enet header |

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

| on Tx |

| UBR |

|

|

|

| Port State |

|

|

|

| queue |

| Port 1 | |

|

|

|

|

|

|

|

|

| Queue 1 | ||

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

| |

| Buffer Base Address |

|

|

|

|

|

|

| |||

4Locate buffer & offset

Length Buffer Offset

2.5StrongARM Core Initialization

On hardware, NetApp_Init is linked into VxWorks, and does the following:

1.Initialize the hardware, including the MACs and PHYs via VxWorks network drivers.

2.Control the baseboard 82559 PCI Ethernet NIC.

Application Note | 19 |

Modified on: 3/20/02,