IXP1200 Network Processor Family ATM

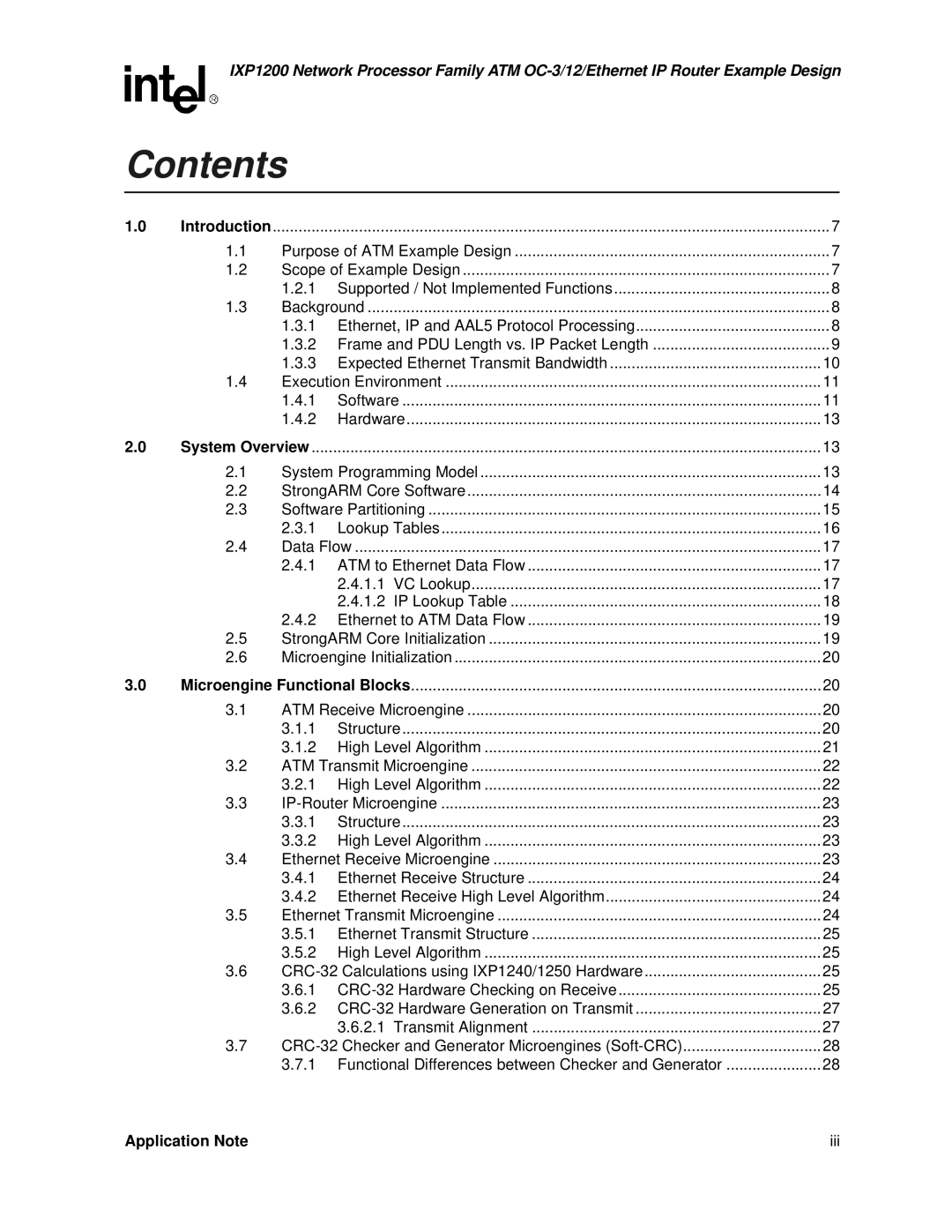

Contents

1.0 | Introduction | ................................................................................................................................. | 7 | |

| 1.1 | Purpose of ATM Example Design | 7 | |

| 1.2 | Scope of Example Design | 7 | |

|

| 1.2.1 Supported / Not Implemented Functions | 8 | |

| 1.3 | Background | 8 | |

|

| 1.3.1 Ethernet, IP and AAL5 Protocol Processing | 8 | |

|

| 1.3.2 Frame and PDU Length vs. IP Packet Length | 9 | |

|

| 1.3.3 Expected Ethernet Transmit Bandwidth | 10 | |

| 1.4 | Execution Environment | 11 | |

|

| 1.4.1 | Software | 11 |

|

| 1.4.2 | Hardware | 13 |

2.0 | System Overview | 13 | ||

| 2.1 | System Programming Model | 13 | |

| 2.2 | StrongARM Core Software | 14 | |

| 2.3 | Software Partitioning | 15 | |

|

| 2.3.1 | Lookup Tables | 16 |

| 2.4 | Data Flow | 17 | |

|

| 2.4.1 ATM to Ethernet Data Flow | 17 | |

|

|

| 2.4.1.1 VC Lookup | 17 |

|

|

| 2.4.1.2 IP Lookup Table | 18 |

|

| 2.4.2 Ethernet to ATM Data Flow | 19 | |

| 2.5 | StrongARM Core Initialization | 19 | |

| 2.6 | Microengine Initialization | 20 | |

3.0 | Microengine Functional Blocks | 20 | ||

| 3.1 | ATM Receive Microengine | 20 | |

|

| 3.1.1 | Structure | 20 |

|

| 3.1.2 | High Level Algorithm | 21 |

| 3.2 | ATM Transmit Microengine | 22 | |

|

| 3.2.1 | High Level Algorithm | 22 |

| 3.3 | 23 | ||

|

| 3.3.1 | Structure | 23 |

|

| 3.3.2 | High Level Algorithm | 23 |

| 3.4 | Ethernet Receive Microengine | 23 | |

|

| 3.4.1 | Ethernet Receive Structure | 24 |

|

| 3.4.2 Ethernet Receive High Level Algorithm | 24 | |

| 3.5 | Ethernet Transmit Microengine | 24 | |

|

| 3.5.1 | Ethernet Transmit Structure | 25 |

|

| 3.5.2 | High Level Algorithm | 25 |

| 3.6 | 25 | ||

|

| 3.6.1 | 25 | |

|

| 3.6.2 | 27 | |

|

|

| 3.6.2.1 Transmit Alignment | 27 |

| 3.7 | 28 | ||

|

| 3.7.1 Functional Differences between Checker and Generator | 28 | |

Application Note | iii |