IXP1200 Network Processor Family ATM

1.2.1Supported / Not Implemented Functions

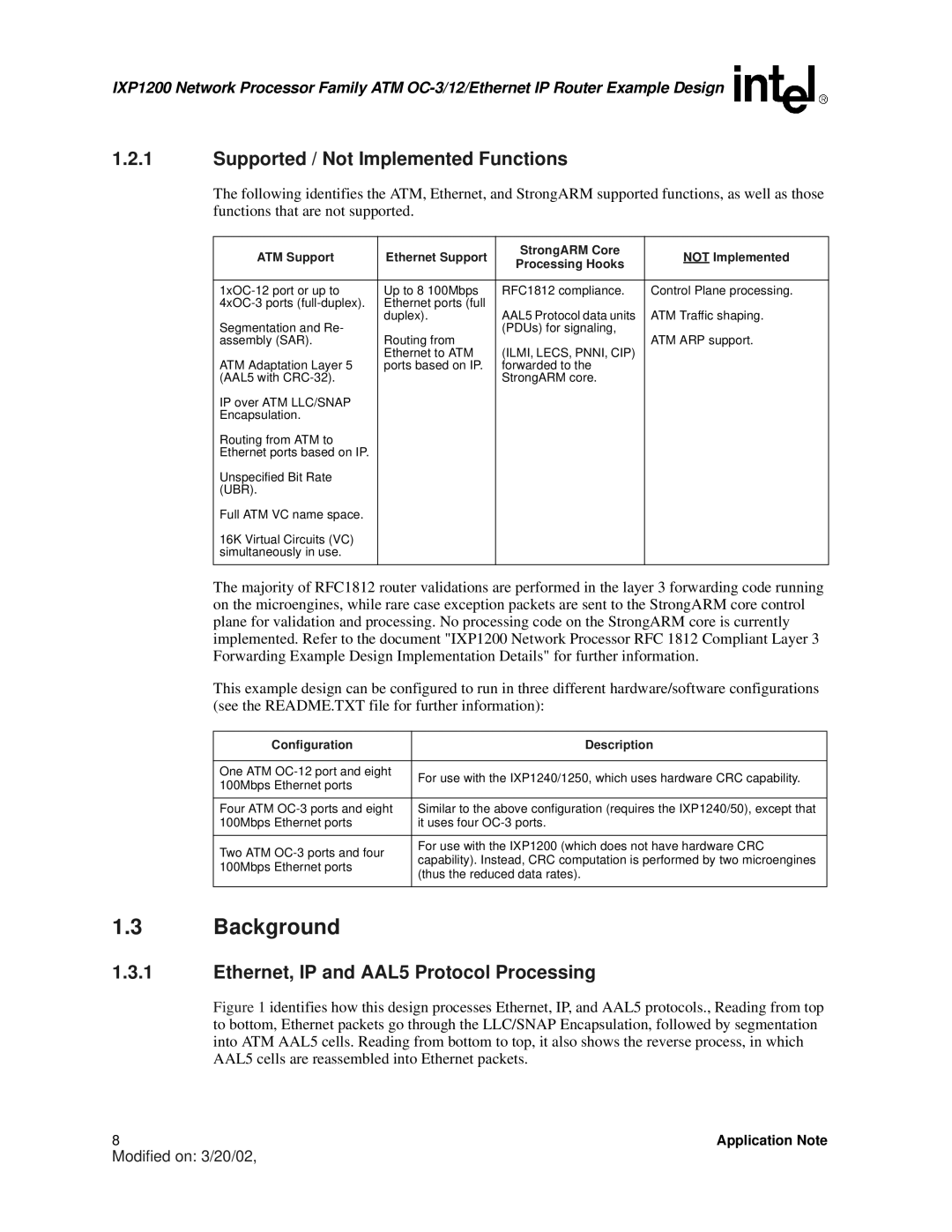

The following identifies the ATM, Ethernet, and StrongARM supported functions, as well as those functions that are not supported.

ATM Support | Ethernet Support | StrongARM Core | NOT Implemented | |

Processing Hooks | ||||

|

|

| ||

|

|

|

| |

Up to 8 100Mbps | RFC1812 compliance. | Control Plane processing. | ||

Ethernet ports (full |

|

| ||

Segmentation and Re- | duplex). | AAL5 Protocol data units | ATM Traffic shaping. | |

| (PDUs) for signaling, |

| ||

assembly (SAR). | Routing from |

| ATM ARP support. | |

ATM Adaptation Layer 5 | Ethernet to ATM | (ILMI, LECS, PNNI, CIP) |

| |

ports based on IP. | forwarded to the |

| ||

(AAL5 with |

| StrongARM core. |

| |

IP over ATM LLC/SNAP |

|

|

| |

Encapsulation. |

|

|

| |

Routing from ATM to |

|

|

| |

Ethernet ports based on IP. |

|

|

| |

Unspecified Bit Rate |

|

|

| |

(UBR). |

|

|

| |

Full ATM VC name space. |

|

|

| |

16K Virtual Circuits (VC) |

|

|

| |

simultaneously in use. |

|

|

| |

|

|

|

|

The majority of RFC1812 router validations are performed in the layer 3 forwarding code running on the microengines, while rare case exception packets are sent to the StrongARM core control plane for validation and processing. No processing code on the StrongARM core is currently implemented. Refer to the document "IXP1200 Network Processor RFC 1812 Compliant Layer 3 Forwarding Example Design Implementation Details" for further information.

This example design can be configured to run in three different hardware/software configurations (see the README.TXT file for further information):

Configuration | Description | |

|

| |

One ATM | For use with the IXP1240/1250, which uses hardware CRC capability. | |

100Mbps Ethernet ports | ||

| ||

|

| |

Four ATM | Similar to the above configuration (requires the IXP1240/50), except that | |

100Mbps Ethernet ports | it uses four | |

|

| |

Two ATM | For use with the IXP1200 (which does not have hardware CRC | |

capability). Instead, CRC computation is performed by two microengines | ||

100Mbps Ethernet ports | ||

(thus the reduced data rates). | ||

| ||

|

|

1.3Background

1.3.1Ethernet, IP and AAL5 Protocol Processing

Figure 1 identifies how this design processes Ethernet, IP, and AAL5 protocols., Reading from top to bottom, Ethernet packets go through the LLC/SNAP Encapsulation, followed by segmentation into ATM AAL5 cells. Reading from bottom to top, it also shows the reverse process, in which AAL5 cells are reassembled into Ethernet packets.

8 | Application Note |

Modified on: 3/20/02,