IXP1200 Network Processor Family ATM

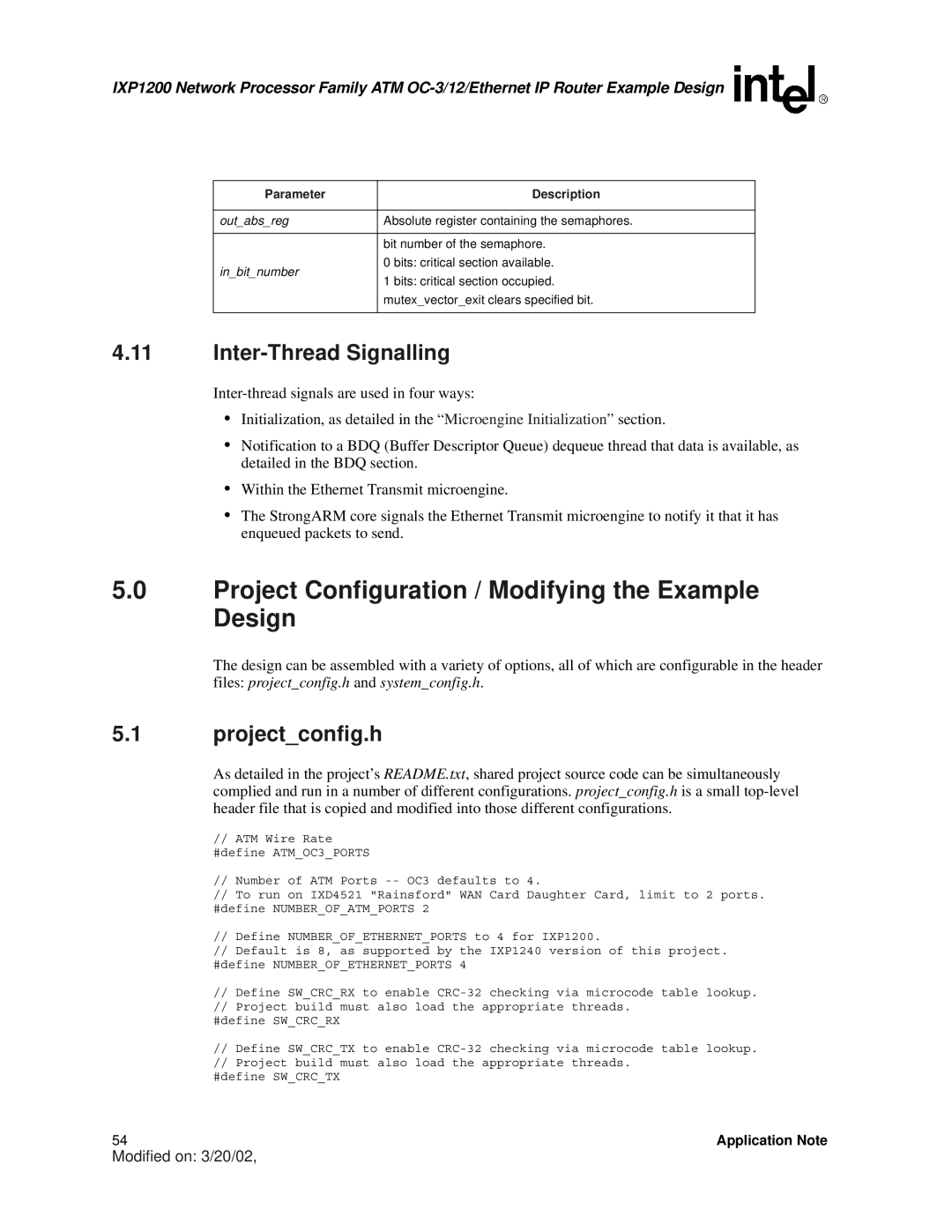

Parameter | Description | |

|

| |

out_abs_reg | Absolute register containing the semaphores. | |

|

| |

| bit number of the semaphore. | |

in_bit_number | 0 bits: critical section available. | |

1 bits: critical section occupied. | ||

| ||

| mutex_vector_exit clears specified bit. | |

|

|

4.11Inter-Thread Signalling

•Initialization, as detailed in the “Microengine Initialization” section.

•Notification to a BDQ (Buffer Descriptor Queue) dequeue thread that data is available, as detailed in the BDQ section.

•Within the Ethernet Transmit microengine.

•The StrongARM core signals the Ethernet Transmit microengine to notify it that it has enqueued packets to send.

5.0Project Configuration / Modifying the Example Design

The design can be assembled with a variety of options, all of which are configurable in the header files: project_config.h and system_config.h.

5.1project_config.h

As detailed in the project’s README.txt, shared project source code can be simultaneously complied and run in a number of different configurations. project_config.h is a small

//ATM Wire Rate #define ATM_OC3_PORTS

//Number of ATM Ports

//To run on IXD4521 "Rainsford" WAN Card Daughter Card, limit to 2 ports. #define NUMBER_OF_ATM_PORTS 2

//Define NUMBER_OF_ETHERNET_PORTS to 4 for IXP1200.

//Default is 8, as supported by the IXP1240 version of this project. #define NUMBER_OF_ETHERNET_PORTS 4

//Define SW_CRC_RX to enable

//Project build must also load the appropriate threads.

#define SW_CRC_RX

//Define SW_CRC_TX to enable

//Project build must also load the appropriate threads.

#define SW_CRC_TX

54 | Application Note |

Modified on: 3/20/02,