IXP1200 Network Processor Family ATM

Register(s) | Description |

|

|

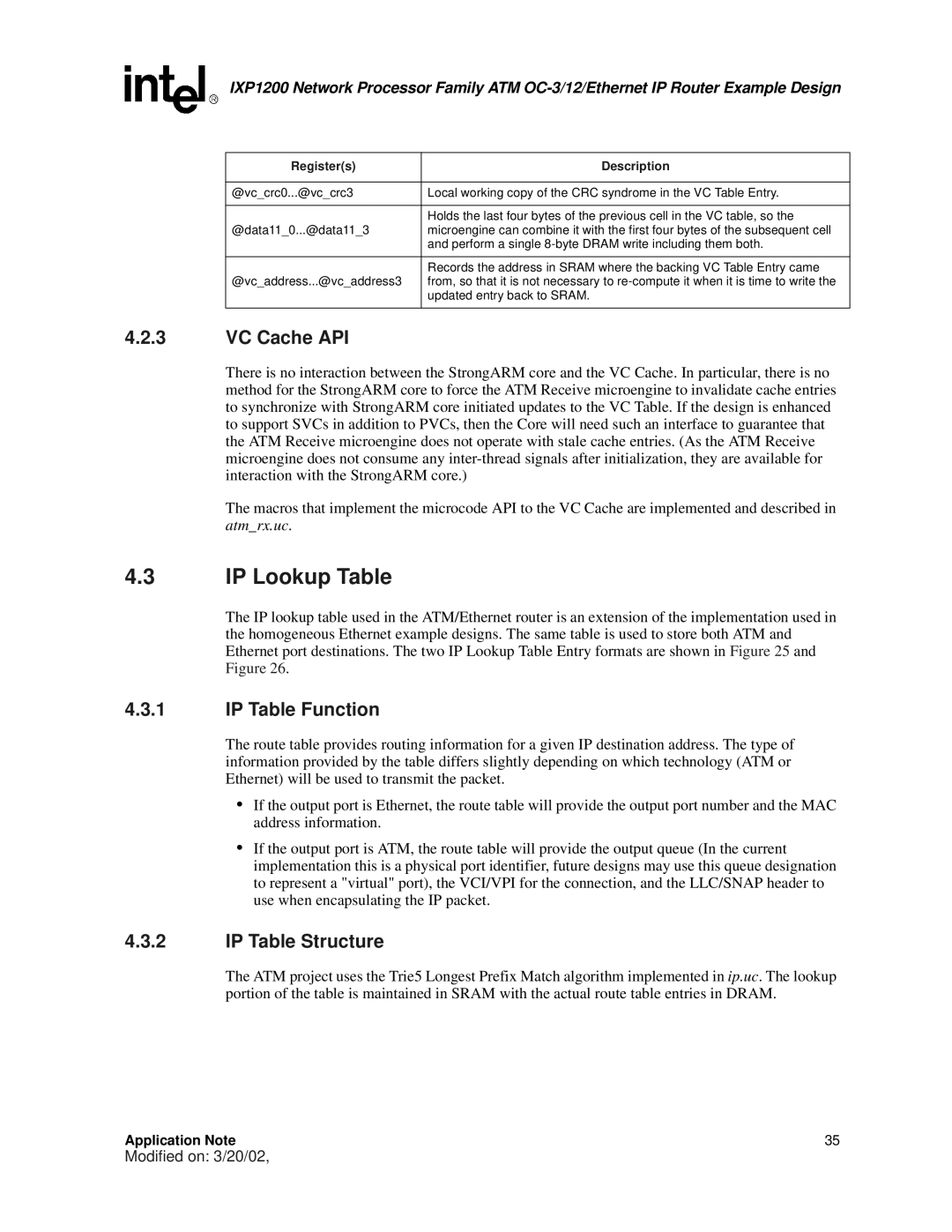

@vc_crc0...@vc_crc3 | Local working copy of the CRC syndrome in the VC Table Entry. |

|

|

| Holds the last four bytes of the previous cell in the VC table, so the |

@data11_0...@data11_3 | microengine can combine it with the first four bytes of the subsequent cell |

| and perform a single |

|

|

| Records the address in SRAM where the backing VC Table Entry came |

@vc_address...@vc_address3 | from, so that it is not necessary to |

| updated entry back to SRAM. |

|

|

4.2.3VC Cache API

There is no interaction between the StrongARM core and the VC Cache. In particular, there is no method for the StrongARM core to force the ATM Receive microengine to invalidate cache entries to synchronize with StrongARM core initiated updates to the VC Table. If the design is enhanced to support SVCs in addition to PVCs, then the Core will need such an interface to guarantee that the ATM Receive microengine does not operate with stale cache entries. (As the ATM Receive microengine does not consume any

The macros that implement the microcode API to the VC Cache are implemented and described in atm_rx.uc.

4.3IP Lookup Table

The IP lookup table used in the ATM/Ethernet router is an extension of the implementation used in the homogeneous Ethernet example designs. The same table is used to store both ATM and Ethernet port destinations. The two IP Lookup Table Entry formats are shown in Figure 25 and Figure 26.

4.3.1IP Table Function

The route table provides routing information for a given IP destination address. The type of information provided by the table differs slightly depending on which technology (ATM or Ethernet) will be used to transmit the packet.

•If the output port is Ethernet, the route table will provide the output port number and the MAC address information.

•If the output port is ATM, the route table will provide the output queue (In the current implementation this is a physical port identifier, future designs may use this queue designation to represent a "virtual" port), the VCI/VPI for the connection, and the LLC/SNAP header to use when encapsulating the IP packet.

4.3.2IP Table Structure

The ATM project uses the Trie5 Longest Prefix Match algorithm implemented in ip.uc. The lookup portion of the table is maintained in SRAM with the actual route table entries in DRAM.

Application Note | 35 |

Modified on: 3/20/02,