IXP1200 Network Processor Family ATM

•For ATM destinations, enqueue to the ATM Transmit microengine, or for software CRC, to the appropriate AAL5

The ETHERNET_LOOPBACK build option enables routing packets from Ethernet Receive ports to Ethernet Transmit ports. This is useful for equipment checkout in the lab. If this option is not defined, packets received from ethernet ports which route to ethernet output ports are discarded with IP_NO_ROUTE exception. If this option is defined, the packets are forwarded as requested.

3.4.1Ethernet Receive Structure

There are four identical threads on each Ethernet receive microengine. Each thread services a specific port and uses a specific RFIFO element.

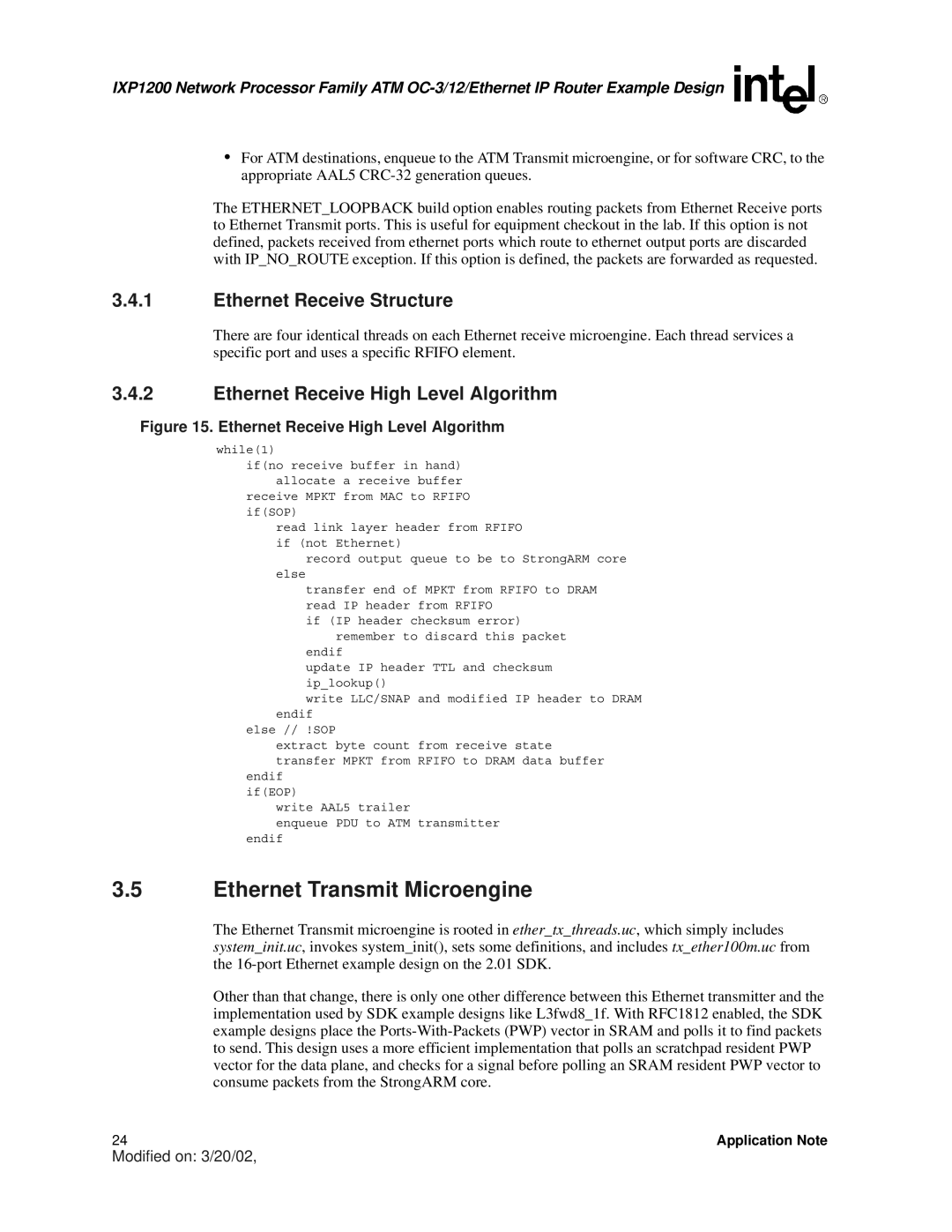

3.4.2Ethernet Receive High Level Algorithm

Figure 15. Ethernet Receive High Level Algorithm

while(1)

if(no receive buffer in hand) allocate a receive buffer

receive MPKT from MAC to RFIFO if(SOP)

read link layer header from RFIFO if (not Ethernet)

record output queue to be to StrongARM core

else

transfer end of MPKT from RFIFO to DRAM read IP header from RFIFO

if (IP header checksum error) remember to discard this packet

endif

update IP header TTL and checksum ip_lookup()

write LLC/SNAP and modified IP header to DRAM endif

else // !SOP

extract byte count from receive state transfer MPKT from RFIFO to DRAM data buffer

endif if(EOP)

write AAL5 trailer

enqueue PDU to ATM transmitter endif

3.5Ethernet Transmit Microengine

The Ethernet Transmit microengine is rooted in ether_tx_threads.uc, which simply includes system_init.uc, invokes system_init(), sets some definitions, and includes tx_ether100m.uc from the

Other than that change, there is only one other difference between this Ethernet transmitter and the implementation used by SDK example designs like L3fwd8_1f. With RFC1812 enabled, the SDK example designs place the

24 | Application Note |

Modified on: 3/20/02,