IXP1200 Network Processor Family ATM

|

|

|

|

|

|

VC Cache enabled. | VC Cache disabled. |

|

|

NUMBER_OF_ATM_PORTS must be 1. | NUMBER_OF_ATM_PORTS may be 1, 2, or 4. |

|

|

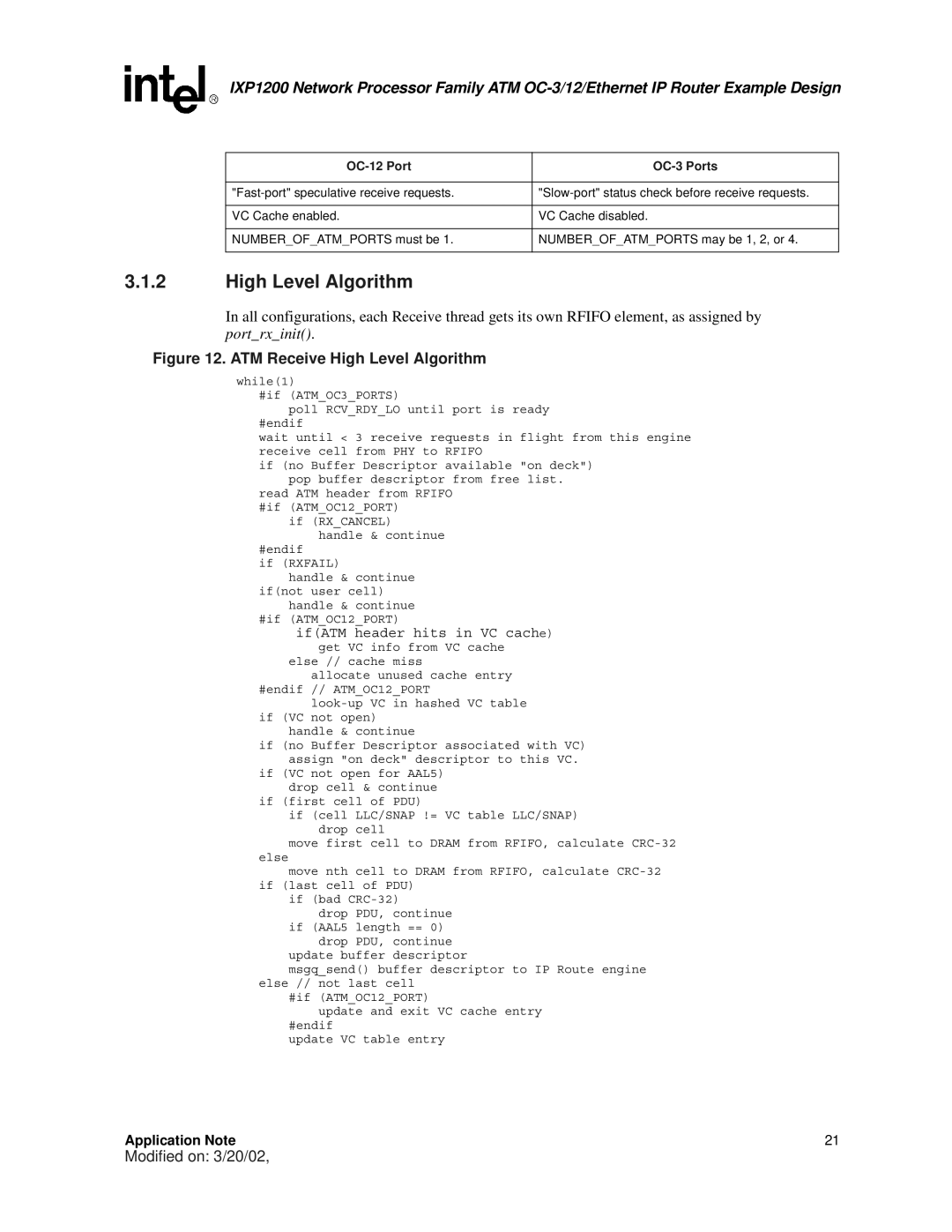

3.1.2High Level Algorithm

In all configurations, each Receive thread gets its own RFIFO element, as assigned by port_rx_init().

Figure 12. ATM Receive High Level Algorithm

while(1)

#if (ATM_OC3_PORTS)

poll RCV_RDY_LO until port is ready #endif

wait until < 3 receive requests in flight from this engine receive cell from PHY to RFIFO

if (no Buffer Descriptor available "on deck")

pop buffer descriptor from free list. read ATM header from RFIFO

#if (ATM_OC12_PORT) if (RX_CANCEL)

handle & continue

#endif

if (RXFAIL)

handle & continue if(not user cell)

handle & continue #if (ATM_OC12_PORT)

if(ATM header hits in VC cache) get VC info from VC cache

else // cache miss

allocate unused cache entry #endif // ATM_OC12_PORT

handle & continue

if (no Buffer Descriptor associated with VC) assign "on deck" descriptor to this VC.

if (VC not open for AAL5) drop cell & continue

if (first cell of PDU)

if (cell LLC/SNAP != VC table LLC/SNAP) drop cell

move first cell to DRAM from RFIFO, calculate

else

move nth cell to DRAM from RFIFO, calculate

if (bad

drop PDU, continue if (AAL5 length == 0)

drop PDU, continue update buffer descriptor

msgq_send() buffer descriptor to IP Route engine else // not last cell

#if (ATM_OC12_PORT)

update and exit VC cache entry #endif

update VC table entry

Application Note | 21 |

Modified on: 3/20/02,