IXP1200 Network Processor Family ATM

For the synchronous

If the dequeuing thread services multiple queues, it can use packetq_send queues and associated dequeue code, or the polled scratchpad

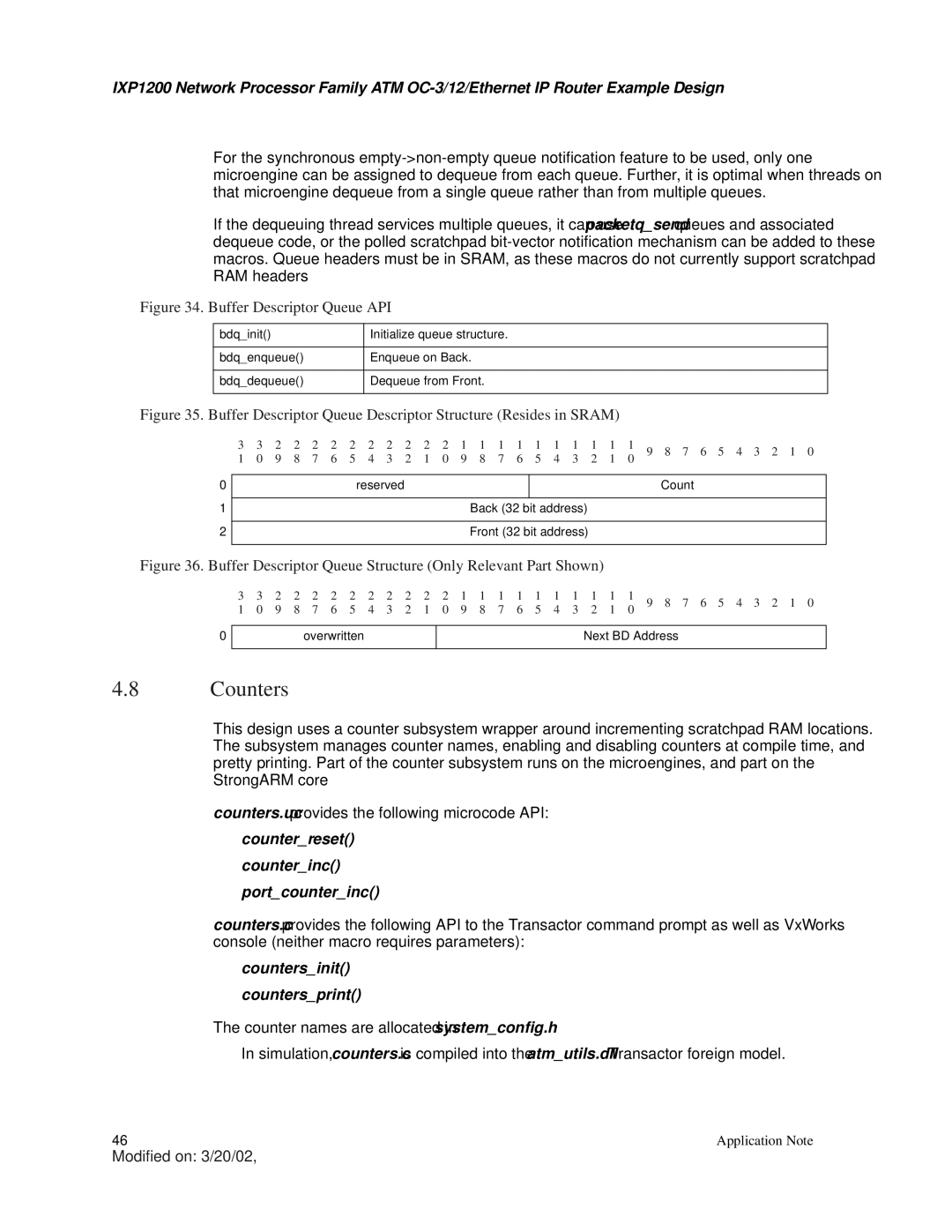

Figure 34. Buffer Descriptor Queue API

bdq_init() | Initialize queue structure. |

|

|

bdq_enqueue() | Enqueue on Back. |

|

|

bdq_dequeue() | Dequeue from Front. |

|

|

Figure 35. Buffer Descriptor Queue Descriptor Structure (Resides in SRAM)

0

1

2

3 | 3 | 2 | 2 | 2 | 2 | 2 | 2 | 2 | 2 | 2 | 2 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

1 | 0 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||||||||||

|

|

|

|

|

|

|

|

|

| |||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

| reserved |

|

|

|

|

|

|

|

|

|

|

|

|

|

| Count |

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

| Back (32 bit address) |

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

| Front (32 bit address) |

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

Figure 36. Buffer Descriptor Queue Structure (Only Relevant Part Shown)

0

3 | 3 | 2 | 2 | 2 | 2 | 2 | 2 | 2 | 2 | 2 | 2 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

1 | 0 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||||||||||

|

|

|

|

|

|

|

|

|

| |||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||

|

|

|

| overwritten |

|

|

|

|

|

|

|

|

|

|

|

| Next BD Address |

|

|

|

|

|

|

|

| |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

4.8Counters

This design uses a counter subsystem wrapper around incrementing scratchpad RAM locations. The subsystem manages counter names, enabling and disabling counters at compile time, and pretty printing. Part of the counter subsystem runs on the microengines, and part on the StrongARM core

counters.uc provides the following microcode API:

•counter_reset()

•counter_inc()

•port_counter_inc()

counters.c provides the following API to the Transactor command prompt as well as VxWorks console (neither macro requires parameters):

•counters_init()

•counters_print()

The counter names are allocated in system_config.h.

•In simulation, counters.c is compiled into the atm_utils.dll Transactor foreign model.

46 | Application Note |

Modified on: 3/20/02,