IXP1200 Network Processor Family ATM

|

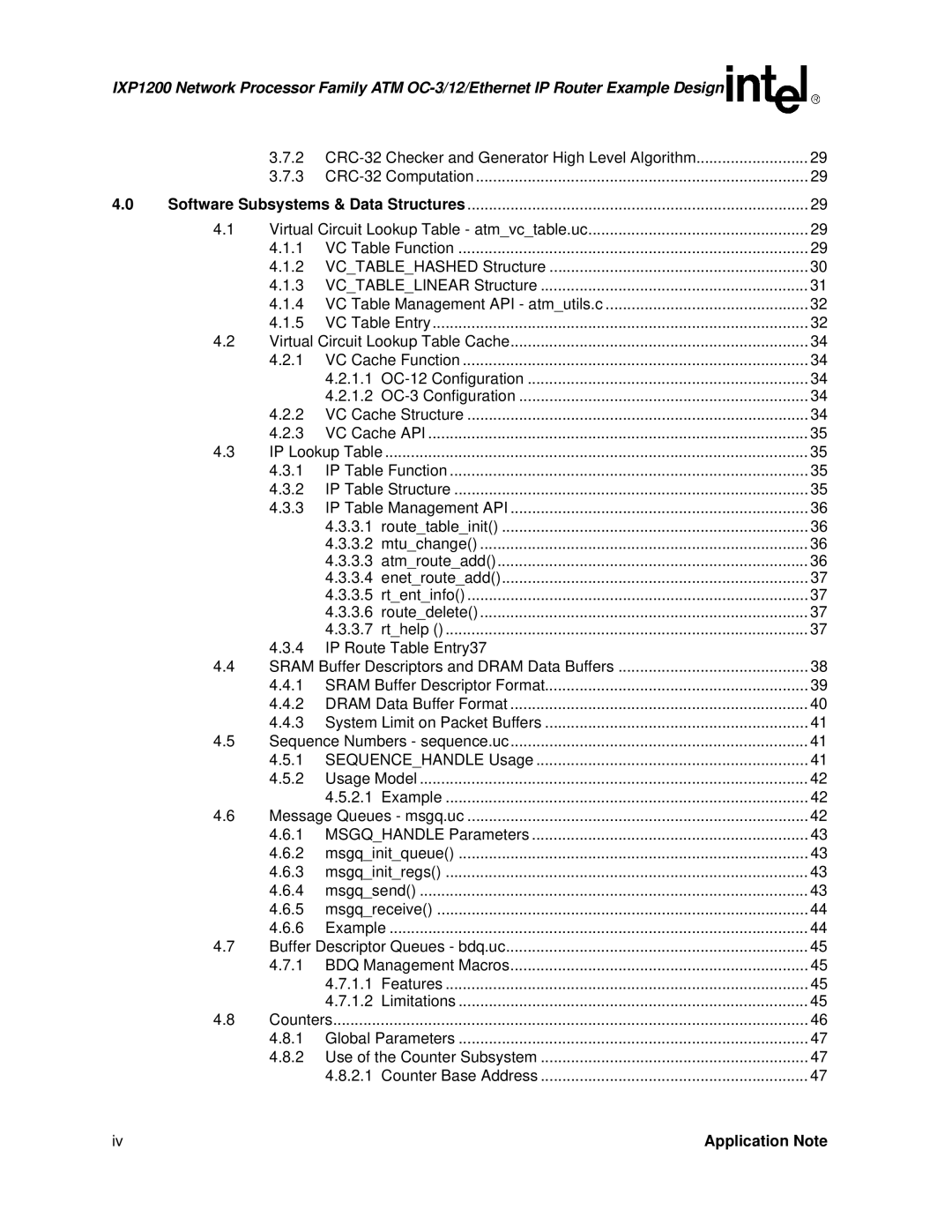

| 3.7.2 | 29 | ||

|

| 3.7.3 | 29 | ||

4.0 | Software Subsystems & Data Structures | 29 | |||

| 4.1 | Virtual Circuit Lookup Table - atm_vc_table.uc | 29 | ||

|

| 4.1.1 | VC Table Function | 29 | |

|

| 4.1.2 | VC_TABLE_HASHED Structure | 30 | |

|

| 4.1.3 | VC_TABLE_LINEAR Structure | 31 | |

|

| 4.1.4 VC Table Management API - atm_utils.c | 32 | ||

|

| 4.1.5 | VC Table Entry | 32 | |

| 4.2 | Virtual Circuit Lookup Table Cache | 34 | ||

|

| 4.2.1 | VC Cache Function | 34 | |

|

|

| 4.2.1.1 | 34 | |

|

|

| 4.2.1.2 | 34 | |

|

| 4.2.2 | VC Cache Structure | 34 | |

|

| 4.2.3 | VC Cache API | 35 | |

| 4.3 | IP Lookup Table | 35 | ||

|

| 4.3.1 | IP Table Function | 35 | |

|

| 4.3.2 | IP Table Structure | 35 | |

|

| 4.3.3 IP Table Management API | 36 | ||

|

|

| 4.3.3.1 route_table_init() | 36 | |

|

|

| 4.3.3.2 mtu_change() | 36 | |

|

|

| 4.3.3.3 atm_route_add() | 36 | |

|

|

| 4.3.3.4 enet_route_add() | 37 | |

|

|

| 4.3.3.5 rt_ent_info() | 37 | |

|

|

| 4.3.3.6 | route_delete() | 37 |

|

|

| 4.3.3.7 rt_help () | 37 | |

|

| 4.3.4 IP Route Table Entry37 |

| ||

| 4.4 | SRAM Buffer Descriptors and DRAM Data Buffers | 38 | ||

|

| 4.4.1 SRAM Buffer Descriptor Format | 39 | ||

|

| 4.4.2 DRAM Data Buffer Format | 40 | ||

|

| 4.4.3 System Limit on Packet Buffers | 41 | ||

| 4.5 | Sequence Numbers - sequence.uc | 41 | ||

|

| 4.5.1 | SEQUENCE_HANDLE Usage | 41 | |

|

| 4.5.2 | Usage Model | 42 | |

|

|

| 4.5.2.1 Example | 42 | |

| 4.6 | Message Queues - msgq.uc | 42 | ||

|

| 4.6.1 | MSGQ_HANDLE Parameters | 43 | |

|

| 4.6.2 msgq_init_queue() | 43 | ||

|

| 4.6.3 msgq_init_regs() | 43 | ||

|

| 4.6.4 | msgq_send() | 43 | |

|

| 4.6.5 | msgq_receive() | 44 | |

|

| 4.6.6 | Example | 44 | |

| 4.7 | Buffer Descriptor Queues - bdq.uc | 45 | ||

|

| 4.7.1 | BDQ Management Macros | 45 | |

|

|

| 4.7.1.1 | Features | 45 |

|

|

| 4.7.1.2 | Limitations | 45 |

| 4.8 | Counters | 46 | ||

|

| 4.8.1 | Global Parameters | 47 | |

|

| 4.8.2 Use of the Counter Subsystem | 47 | ||

|

|

| 4.8.2.1 Counter Base Address | 47 | |

iv | Application Note |