IXP1200 Network Processor Family ATM

3.2ATM Transmit Microengine

The ATM Transmit microengine is an AAL5 Unspecified Bit Rate (UBR) Transmitter that uses a single microengine to move cells at

The transmitter consumes PDUs one at a time from beginning to end, resulting in an output stream in which cells from the same PDU are transmitted

The transmitter is implemented with 3 identical fill threads. Unlike the Ethernet transmitter, the ATM transmitter does not have a thread dedicated to scheduling the work of the fill threads. Rather, the fill threads use shared absolute registers to act as a "distributed scheduler". The fourth thread could also be enabled as a fill thread, but is not needed at the wire rates in this design.

In IXP1240/1250 hardware CRC configurations, the ATM Transmitter generates

32 is computed by a dedicated

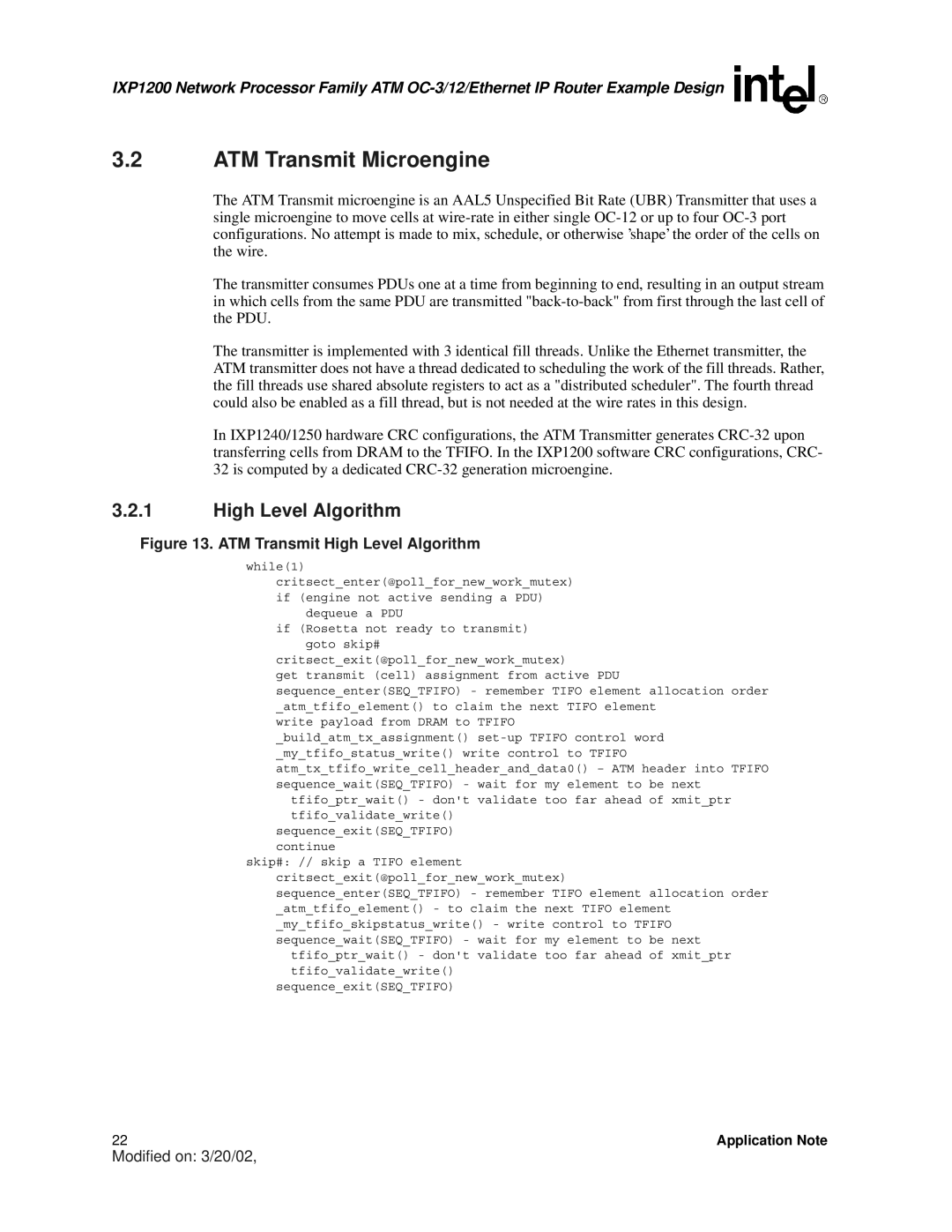

3.2.1High Level Algorithm

Figure 13. ATM Transmit High Level Algorithm

while(1) critsect_enter(@poll_for_new_work_mutex) if (engine not active sending a PDU)

dequeue a PDU

if (Rosetta not ready to transmit) goto skip#

critsect_exit(@poll_for_new_work_mutex)

get transmit (cell) assignment from active PDU

sequence_enter(SEQ_TFIFO) - remember TIFO element allocation order _atm_tfifo_element() to claim the next TIFO element

write payload from DRAM to TFIFO

_build_atm_tx_assignment()

tfifo_ptr_wait() - don't validate too far ahead of xmit_ptr tfifo_validate_write()

sequence_exit(SEQ_TFIFO) continue

skip#: // skip a TIFO element critsect_exit(@poll_for_new_work_mutex) sequence_enter(SEQ_TFIFO) - remember TIFO element allocation order _atm_tfifo_element() - to claim the next TIFO element _my_tfifo_skipstatus_write() - write control to TFIFO sequence_wait(SEQ_TFIFO) - wait for my element to be next

tfifo_ptr_wait() - don't validate too far ahead of xmit_ptr tfifo_validate_write()

sequence_exit(SEQ_TFIFO)

22 | Application Note |

Modified on: 3/20/02,