IXP1200 Network Processor Family ATM

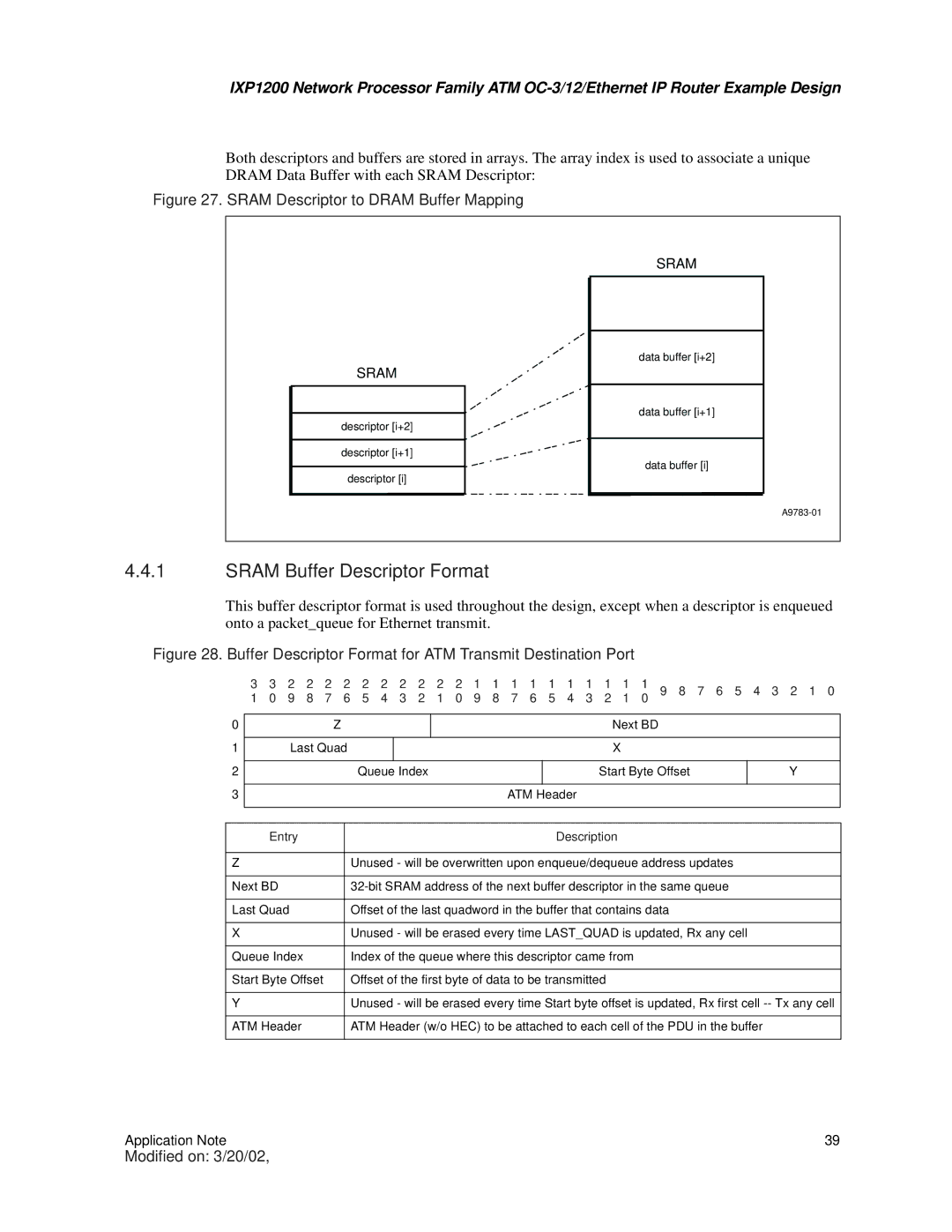

Both descriptors and buffers are stored in arrays. The array index is used to associate a unique DRAM Data Buffer with each SRAM Descriptor:

Figure 27. SRAM Descriptor to DRAM Buffer Mapping

SRAM |

data buffer [i+2] |

SRAM |

data buffer [i+1] |

descriptor [i+2] |

descriptor [i+1] |

data buffer [i] |

descriptor [i] |

4.4.1SRAM Buffer Descriptor Format

This buffer descriptor format is used throughout the design, except when a descriptor is enqueued onto a packet_queue for Ethernet transmit.

Figure 28. Buffer Descriptor Format for ATM Transmit Destination Port

0

1

2

3

3 | 3 | 2 | 2 | 2 | 2 | 2 | 2 | 2 | 2 | 2 | 2 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

1 | 0 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||||||||||

|

|

|

|

|

|

|

|

|

| |||||||||||||||||||||||

|

|

|

|

| Z |

|

|

|

|

|

|

|

|

|

|

|

|

|

| Next BD |

|

|

|

|

|

|

|

|

|

| ||

|

| Last Quad |

|

|

|

|

|

|

|

|

|

|

|

|

|

| X |

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

| Queue Index |

|

|

|

|

|

|

|

|

| Start Byte Offset |

|

|

|

|

| Y |

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| ATM Header |

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

Entry | Description |

Z | Unused - will be overwritten upon enqueue/dequeue address updates |

Next BD | |

Last Quad | Offset of the last quadword in the buffer that contains data |

X | Unused - will be erased every time LAST_QUAD is updated, Rx any cell |

Queue Index | Index of the queue where this descriptor came from |

Start Byte Offset | Offset of the first byte of data to be transmitted |

Y | Unused - will be erased every time Start byte offset is updated, Rx first cell |

ATM Header | ATM Header (w/o HEC) to be attached to each cell of the PDU in the buffer |

Application Note | 39 |

Modified on: 3/20/02,