IXP1200 Network Processor Family ATM

... ; process the message, threads may get out of order. move(message, $xfer)

sequence_wait(MY_SEQUENCE) ; wait until it is my turn to send msgq_send(message, $xfer, MY_MSGQ, ctx_swap)

.if (message != 0) counter_inc(OUTPUT_MSGQ_IS_FULL) ; record failure buf_push(message, ...)

;if message is descriptor, return it...

.endif

sequence_exit(MY_SEQUENCE)

;allow next thread through sequence_wait()

4.7Buffer Descriptor Queues - bdq.uc

This design uses a generic buffer descriptor queuing subsystem to pass data between microengines. This section describes the facility so that it will be clear when it is applied throughout the design.

Buffer Descriptor Queues (BDQs) are analogous to packet queues, as defined in packetq.uc and tx.uc. BDQs support cached dequeues, and are therefore more efficient when a microengine dequeues from a small number of queues.

4.7.1BDQ Management Macros

Buffer descriptor queue management macros are used for queueing SRAM buffer descriptors between microengines.

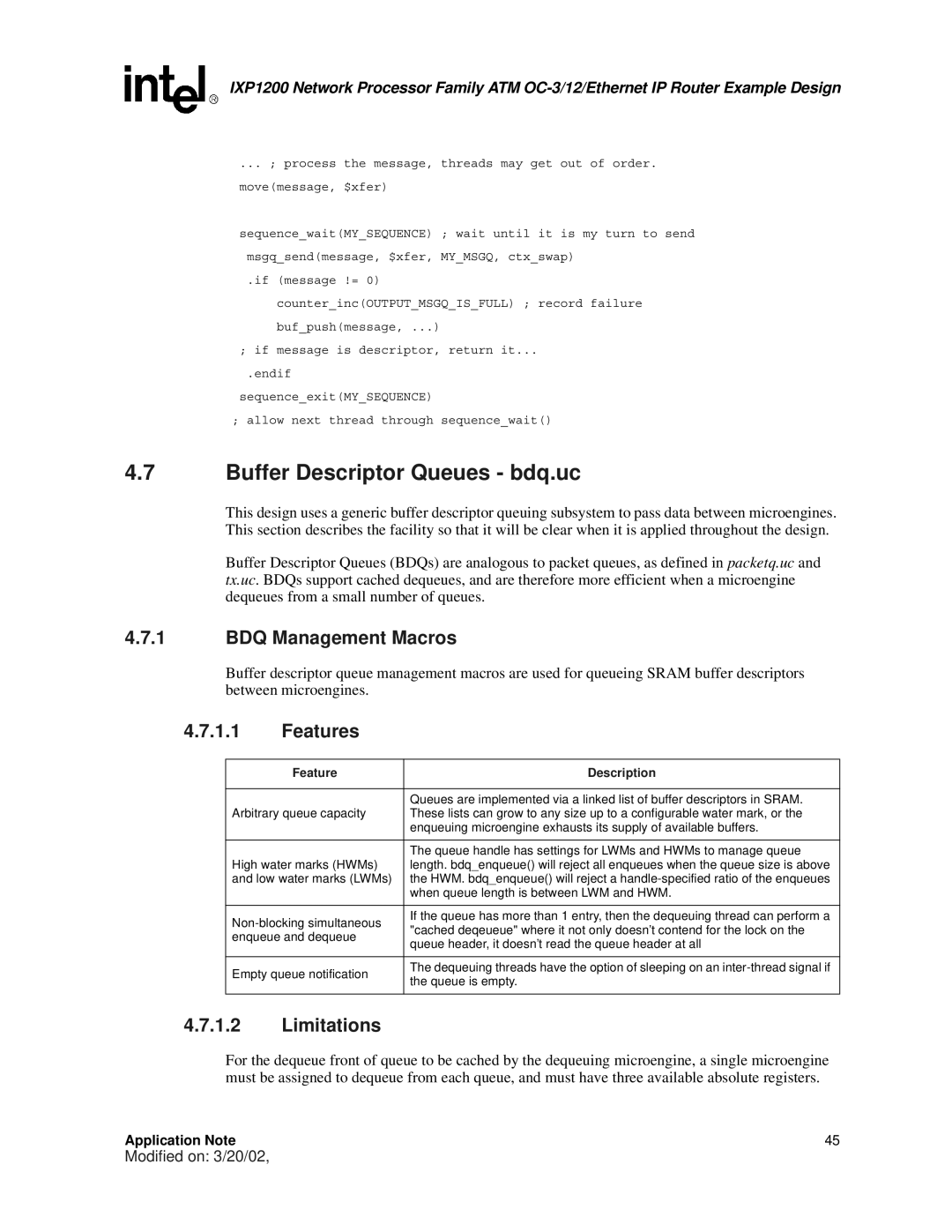

4.7.1.1 | Features |

| |

|

|

|

|

|

| Feature | Description |

|

|

|

|

|

|

| Queues are implemented via a linked list of buffer descriptors in SRAM. |

| Arbitrary queue capacity | These lists can grow to any size up to a configurable water mark, or the | |

|

|

| enqueuing microengine exhausts its supply of available buffers. |

|

|

|

|

|

|

| The queue handle has settings for LWMs and HWMs to manage queue |

| High water marks (HWMs) | length. bdq_enqueue() will reject all enqueues when the queue size is above | |

| and low water marks (LWMs) | the HWM. bdq_enqueue() will reject a | |

|

|

| when queue length is between LWM and HWM. |

|

|

|

|

| If the queue has more than 1 entry, then the dequeuing thread can perform a | ||

| "cached deqeueue" where it not only doesn’t contend for the lock on the | ||

| enqueue and dequeue | ||

| queue header, it doesn’t read the queue header at all | ||

|

|

| |

|

|

|

|

| Empty queue notification | The dequeuing threads have the option of sleeping on an | |

| the queue is empty. | ||

|

|

| |

|

|

|

|

4.7.1.2Limitations

For the dequeue front of queue to be cached by the dequeuing microengine, a single microengine must be assigned to dequeue from each queue, and must have three available absolute registers.

Application Note | 45 |

Modified on: 3/20/02,