Programming Considerations

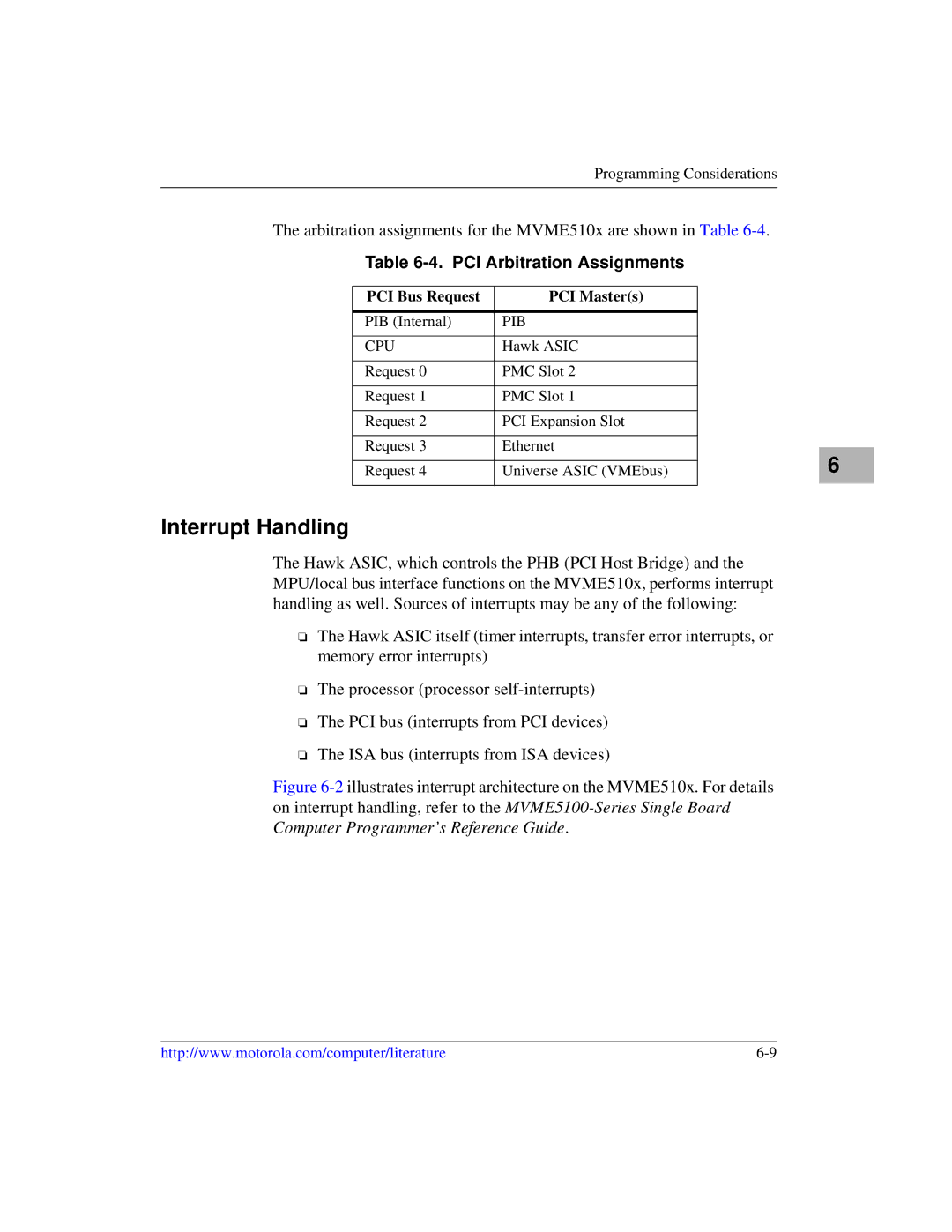

The arbitration assignments for the MVME510x are shown in Table

Table 6-4. PCI Arbitration Assignments

PCI Bus Request | PCI Master(s) |

|

| |

|

|

|

| |

PIB (Internal) | PIB |

|

| |

|

|

|

| |

CPU | Hawk ASIC |

|

| |

|

|

|

| |

Request 0 | PMC Slot 2 |

|

| |

|

|

|

| |

Request 1 | PMC Slot 1 |

|

| |

|

|

|

| |

Request 2 | PCI Expansion Slot |

|

| |

|

|

|

| |

Request 3 | Ethernet |

|

| |

6 | ||||

|

|

| ||

Request 4 | Universe ASIC (VMEbus) |

| ||

|

|

|

|

Interrupt Handling

The Hawk ASIC, which controls the PHB (PCI Host Bridge) and the MPU/local bus interface functions on the MVME510x, performs interrupt handling as well. Sources of interrupts may be any of the following:

❏The Hawk ASIC itself (timer interrupts, transfer error interrupts, or memory error interrupts)

❏The processor (processor

❏The PCI bus (interrupts from PCI devices)

❏The ISA bus (interrupts from ISA devices)

Figure 6-2 illustrates interrupt architecture on the MVME510x. For details on interrupt handling, refer to the MVME5100-Series Single Board Computer Programmer’s Reference Guide.

http://www.motorola.com/computer/literature |