KFM4GH6Q4M KFN8GH6Q4M KFKAGH6Q4M

Corrected errata

Initial issue

Revision No History Draft Date

Remark

Oct

Ordering Information

General Overview

System Hardware

Product Features

Device Architecture

Device Performance

Definitions

Detailed Product Description

1 4Gb KFM4GH6Q4M / 8Gb KFN8GH6Q4M

Pin Configuration

63ball, 10mm x 13mm x max 1.0mmt , 0.8mm ball pitch FBGA4Gb

TOP VIEW, Balls Facing Down 63ball Fbga OneNAND Chip

2 16Gb Product KFKAGH6Q4M TBD

Interrupt

Pin Description

Multiplexed Address/Data bus

Register read cycles

OTP

Block Diagram

Memory Array Organization

Internal Nand Array Memory Organization

BlockMLC

Sector

BlockSLC

Internal Nand Array Memory

BootRAM 1KB DataRAM0 2KB DataRAM1 2KB

Boot code Nand Array OTP Block

External BufferRAM Memory

256KB

Memory Map

Block Block Address Size

0000h

Block Block Address

Block161

Block128

Block160

Block129

Block240 00F0h

Block238 00EEh

Block290 0122h Block259

Block256

Block288 0120h Block257

Block289 0121h Block258

Block354 0162h Block323

Block320

Block352 0160h Block321

Block353 0161h Block322

Block417

Block384

Block416

Block385

Block496 01F0h

Block494 01EEh

Block546 0222h Block515

Block512

Block544 0220h Block513

Block545 0221h Block514

Block610 0262h Block579

Block576

Block608 0260h Block577

Block609 0261h Block578

Block673

Block640

Block672

Block641

Block752 02F0h

Block750 02EEh

Block802 0322h Block771

Block768

Block800 0320h Block769

Block801 0321h Block770

Block866 0362h Block835

Block832

Block864 0360h Block833

Block865 0361h Block834

Block929

Block896

Block928

Block897

Block1008 03F0h

Block1006 03EEh

Byte

Internal Memory Spare Area Assignment

Area

256W

Division Address Size Usage Description

External Memory BufferRAM Address Map

DataRAMMain area

BootRAMMain area

BootRAMSpare area

External Memory Map Detail Information

Buf Word Byte

External Memory Spare Area Assignment

10074h 803Bh 10076h 803Ch 10078h 803Dh

10054h 802Bh 10056h 802Ch 10058h 802Dh

4bit ECC parity values 8046h 1008Ch 8047h 1008Eh

10094h 804Bh 10096h 804Ch 10098h 804Dh

DataS

10090h BIBad block Information

10092h Managed by internal ECC logic

Register Address Map

Registers

Address Name Host Description

Device Identification

Device ID Default

Manufacturer ID Register F000h R

Device ID Register F001h R

Data Buffer Size Register F003h R

Version ID Register F002h

This register is reserved for future use

Amount of Buffers Register F005h R

Boot Buffer Size Register F004h R

Technology Register F006h R

Start Address2 Register F101h R/W

Start Address1 Register F100h R/W

11~15 Start Address3~7 Register F102h~F106h

Start Buffer Register F200h R/W

Start Address8 Register F107h R/W

Sector allocation according to BSCCASE3 FSA=10 BSC =

Sector allocation according to BSCCASE1 FSA=00 BSC =

BSC =111

Sector allocation according to BSCCASE2 FSA=01 BSC =

Operation

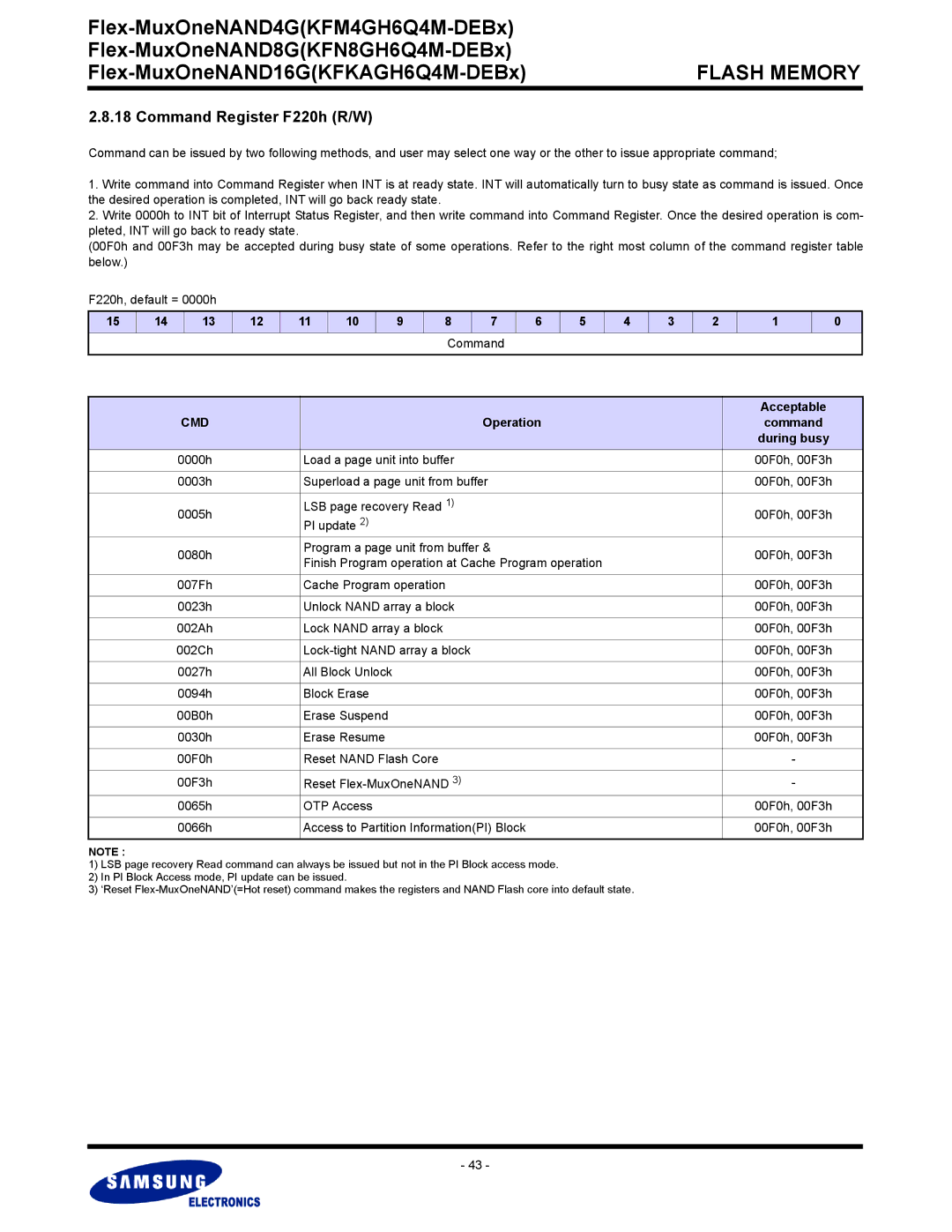

Command Register F220h R/W

Acceptable

CMD

Write command into INT will automatically

Two Methods to Clear Interrupt Register in Command Input

Interrupt Register

Brwl

System Configuration 1 Register F221h R, R/W

RDY Polarity RDYpol Information7

Burst Length BL

Burst LengthMain Burst LengthSpare

Burst Length BL Information119

Iobe

Bwps

Write Mode WM

Write Mode Information1 Definition Description

MRSMode Register Setting Description

Otpl Otpbl

System Configuration 2 Register F222h

Controller Status Register F240h R

PIL

Otpl

INT

Interrupt Status Register F241h R/W

Rsti

RI Interrupt Status Conditions

WI Interrupt Status Conditions Default State Valid

EI Interrupt Status Conditions Default State Valid

Read Interrupt RI

SBA

Start Block Address Register F24Ch R/W

Start Block Address Register F24Dh R/W

Nand Flash Write Protection Status Register F24Eh R

ECC Status Register 1 FF00h R

ECC Status Register 2 FF01h R FF01h, default = 0000h

ECC Status Register 3 FF02h R FF02h, default = 0000h

ECC Status Register 4 FF03h R FF03h, default = 0000h

Reset Flex-MuxOneNAND Add BP1 Data 00F0h

Command Based Operation

Add Data 00E0h 0000h3 Read Identification Data XXXXh4 0090h

Identification Data Description Address Data Out

Reset Flex-MuxOneNAND Command

Load Data Into Buffer Command

Read Identification Data Command

Operation ADQ0~15

Device Bus Operation

CLK AVD

BP-F0h

Reset Mode Operation

Nand Flash Core Reset Mode Operation

Cold Reset Mode Operation

Warm Reset Mode Operation

Hot Reset Mode Operation

Nand Array Write Protection States

BootRAM Write Protection Operation

Write Protection Operation

Nand Flash Array Write Protection Operation

Unlocked Nand Array Write Protection State

Unlocked Unlock Command Sequence

Unlocked All Block Unlock Command Sequence

Locked Lock Command Sequence

Locked-tight Nand Array Write Protection State

Nand Flash Array Write Protection State Diagram

Locked-tight Lock-Tight Command Sequence

Start block address+Lock-tight block command 002Ch

DQ10=0?

Samsung strongly recommends to follow the above flow chart

Lock/Unlock/Lock-TightError completed

DBS, DFS is for DDP

All Block Unlock Completed

Load Operation

Data Protection During Power Down Operation

Superload Operation

LSB Page Recovery Read

Synchronous Read Mode Operation RM=1, WM=X

Asynchronous Read Mode Operation RM=0, WM=0

Read Operation

2.2 4-, 8-, 16-, 32-Word Linear Burst Read Operation

Continuous Linear Burst Read Operation

Reserved area is not available on Synchronous read

Programmable Burst Read Latency Operation

Output Disable Mode Operation

Handshaking Operation

Synchronous WriteRM=1, WM=1

See Timing Diagram 6.6, 6.7

MLC Block

Program Operation

Addressing for program operation

Data register

Paired Page Address

Paired Page Address Information

Flash Memory

Block including the page in error and copy

If program operation results in an error, map out

DBS, DFS is for DDP Target data to another block

Interrupt register must not be written

Program Interleave can work in Auto INT

DBS, DFS is for DDP

Sector0 Sector7

Cache Program Operation

Add F101h DQ=DBS Add DataRAM DQ=Data4KB

Cache Program Operation Flow Diagram

Program Error

Last PGM?

Interleave Cache Program Operation

If program operation

Results in an error

Block

Write ‘DFS , FBA’ o f Fla sh

Copy back completed Copy back Error

Copy-Back Program Operation with Random Data Input

Add F241h DQ=0000h DQ=Data

Erase Operation

Erase Error

Block Erase Operation

Add F101h DQ=DBS Add F241h DQ=5=EI

Erase Interleave1 @DDP Flow Chart

INT=1Ready Erase Error

Add F100h DQ=DFS*, FBA Add F101h DQ=DBS

Erase Suspend During a Block Erase Operation

Erase Suspend / Erase Resume Operation

Erase Resume

Partition Information PI Block SLC Only

PI Block Boundary Information setting steps

PI Block Boundary Information setting

PI Block Boundary Information setting Flow Chart

PI Block Access mode entry Flow Chart

PI Block Access mode entry

PI Block Erase

PI Block Erase Operation Flow Chart In PI Block Access Mode

Erasing the PI Area

Locking the PI

PI Block Program Operation

Memory location in the PI area can be program

Programming the PI Area

Update the PI Area

PI Update

Add F241h DQ15=INT PI updated

PI Block Load Operation

OTP Operation SLC only

1st Block OTP Area Structure

OTP Block Area Structure

OTP Exit

OTP Block Load Operation

Programming the OTP Area

OTP Block Program Operation

OTPL=0? YES

OTP Block Program Operation Flow Chart

Do Cold/Warm/Hot Nand Flash Core reset OTP Exit

Add DP DQ=Data-in

Locking the OTP

OTP Block Lock Operation

OTP Lock Operation Steps

Automatically Updated

Add F241h DQ15=INT Do Cold reset

Add F241h DQ15=INT Write Data into DataRAM3 Add 1st Word

Locking the 1st Block OTP

13.4 1st Block OTP Lock Operation

1st Block OTP Lock Operation Steps

100

Locking the OTP and 1st Block OTP

OTP and 1st Block OTP Lock Operation

OTP and 1st Block OTP simultaneous Lock Operation Steps

102

Progress Data Loading Don’t Care

14 DQ6 Toggle Bit

Status DQ15~DQ7

DQ6 DQ5~DQ0

ECC Bypass Operation

ECC Operation

Invalid Block Identification Table Operation

Invalid Block Operation

Invalid Block Table Creation Flow Chart Start

Invalid Block Replacement Operation

1st Block B 1th Nth 107

Block Replacement Operation Sequence

Block a

1st 1th Nth

Operating Conditions

Absolute Maximum Ratings

KFM4GH6Q4M

Parameter

DC Characteristics

Test Conditions

DDP QDP

Valid Block Characteristics

AC Test Conditions

Device Capacitance

Max Min

AC Characteristics for Synchronous Burst Read

See Timing Diagrams 6.1 Parameter

66MHz 83MHz Unit

Min Max

AC Characteristics for Asynchronous Read

KFN8GH6Q4M

KFKAGH6Q4MTBD

AC Characteristics for Burst Write Operation

AC Characteristics for Asynchronous Write

See Timing Diagrams Parameter Symbol Min Max Unit

114

AC Characteristics for Load/Program/Erase Performance

AC Characteristics for INT Auto Mode

200

RDY

8-Word Linear Burst Read Mode with Wrap Around

Continuous Linear Burst Read Mode with Wrap Around

CLK

Asynchronous Read VA Transition After AVD Low

See AC Characteristics Table DQ0 DQ15

Asynchronous Read VA Transition Before

Low

Hi-Z

Asynchronous Write

ADQ15-ADQ0

Valid WD

118

8-Word Linear Burst Write Mode

Burst Write Operation followed by Burst Read

≈D7

119

Start Initial Burst Write Operation

Completed Da+n

See AC Characteristics .7 and Table

Load Command Sequence last two cycles Read Data

Load Operation Timing

Superload Operation Timing

Program Operation Timing

Program Command Sequence last two cycles

122

Ongoing Status

Timing

Ongoing Status INT bit

Interleave Cache Program Operation

ADQ0~

ADQ15

Block Erase Operation Timing

Erase Command Sequence

125

Cold Reset Timing

CE, OE

Warm Reset Timing

127

Flex-MuxOneNAND

Hot Reset Timing

ADQi

ADQi

Nand Flash Core Reset Timing

Data Protection Timing During Power Down

Flex-MuxOneNAND Operation or Idle Nand Flash Core reset

RDY

Status RD Hi-Z

130

Write command into Command Register INT will automatically

INT auto mode

131

132

Methods of Determining Interrupt Status

INT Type Mono INT Type DDP

General Operation DQ type

Asynchronous Mode Using the INT Pin

Synchronous Mode Using the INT Pin

INT Pin to a Host General Purpose I/O

134

Polling the Interrupt Register Status Bit

Determining Rp Value DDP, QDP Only

INT pol = ‘High’ Default

Rpohm

Vss KFN8GH6Q4M @ Vcc = 1.8V, Ta = 25C , CL = 30pF

INT pol = ‘Low’

Vcc or Vccq

Ready

Boot Loaders in Flex-MuxOneNAND Description

Boot Sequence

Boot Loaders in Flex-MuxOneNAND

Boot Sequence

NBL2

NBL3

BL2

BL1

Data Register

Partition of Flex-MuxOneNAND

MLC Partition +1 ~ n-1 Blocks

Last Block Address First Block Address

DDPDual Die Package

DDP and QDP Description

QDPQuad Die Package

8G product KFN8GH6Q4M

4G product KFM4GH6Q4M

141

142

16G product KFKAGH6Q4M