TD1_CLK27 | PIN_G15 | TV Decoder 1 Clock Input. |

|

|

|

TD1_RESET_N | PIN_D14 | TV Decoder 1 Reset |

|

|

|

TD2_D[0] | PIN_C10 | TV Decoder 2 Data[0] |

|

|

|

TD2_D[1] | PIN_A9 | TV Decoder 2 Data[1] |

|

|

|

TD2_D[2] | PIN_B9 | TV Decoder 2 Data[2] |

|

|

|

TD2_D[3] | PIN_C9 | TV Decoder 2 Data[3] |

|

|

|

TD2_D[4] | PIN_A8 | TV Decoder 2 Data[4] |

|

|

|

TD2_D[5] | PIN_B8 | TV Decoder 2 Data[5] |

|

|

|

TD2_D[6] | PIN_A7 | TV Decoder 2 Data[6] |

|

|

|

TD2_D[7] | PIN_B7 | TV Decoder 2 Data[7] |

|

|

|

TD2_HS | PIN_E15 | TV Decoder 2 H_SYNC |

|

|

|

TD2_VS | PIN_D15 | TV Decoder 2 V_SYNC |

|

|

|

TD2_CLK27 | PIN_H15 | TV Decoder 2 Clock Input. |

|

|

|

TD2_RESET_N | PIN_B10 | TV Decoder 2 Reset |

|

|

|

I2C_SCLK | PIN_J18 | I2C Data |

|

|

|

I2C_SDAT | PIN_H18 | I2C Clock |

|

|

|

Table 5.16. TV Decoder pin assignments.

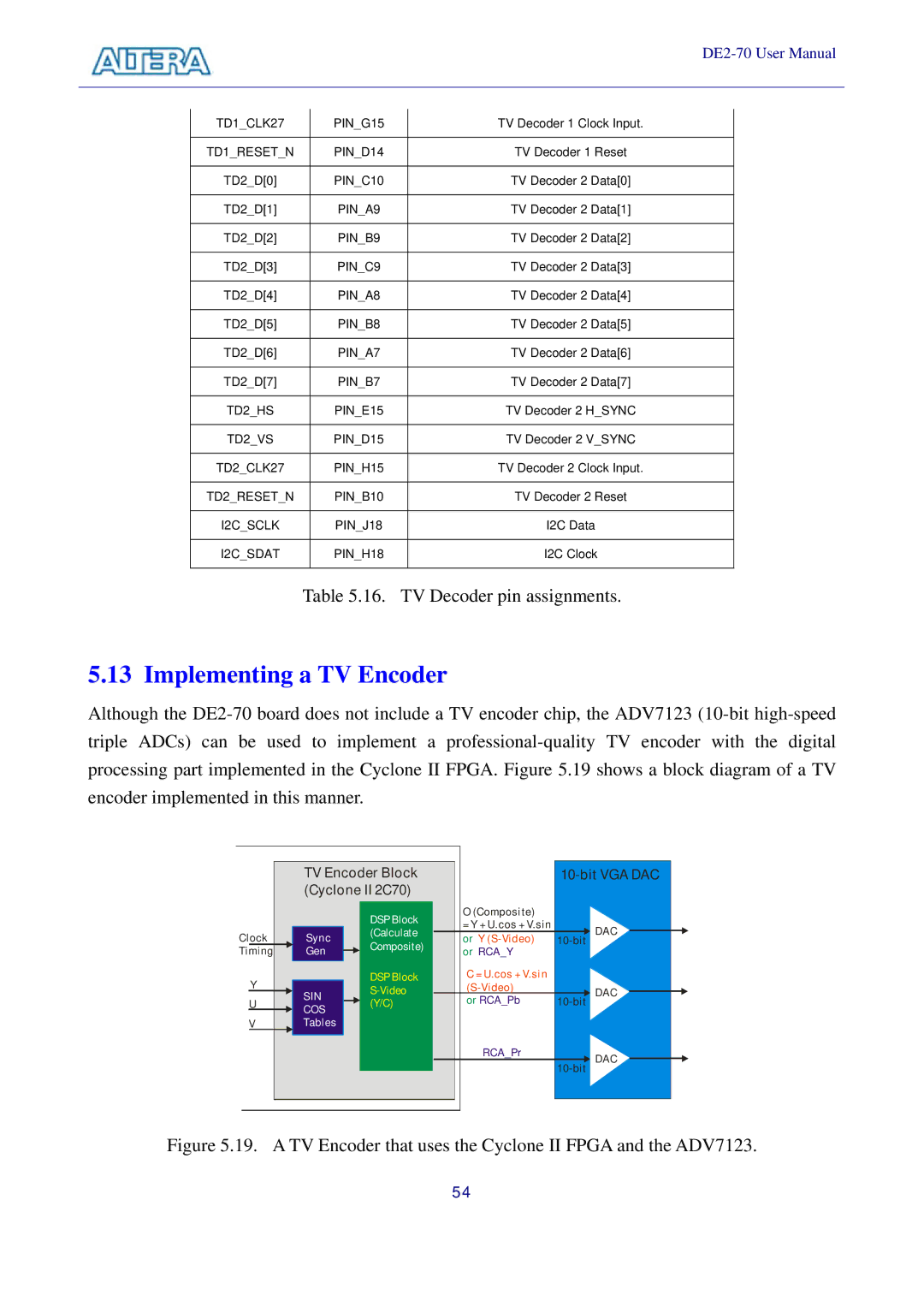

5.13 Implementing a TV Encoder

Although the

TV Encoder Block

(Cyclone II 2C70)

DSP Block

Clock Sync (Calculate

Timing Gen ![]() Composite)

Composite)

Y |

|

| DSP Block |

SIN |

| ||

|

| ||

U |

| (Y/C) | |

COS |

| ||

|

|

|

VTables

|

|

| ||||

O (Composite) |

|

|

|

|

|

|

= Y + U.cos + V.sin |

|

| DAC |

|

| |

or Y |

|

|

| |||

or RCA_Y |

|

|

|

|

|

|

C = U.cos + V.sin |

|

|

|

|

|

|

|

| DAC |

|

|

| |

or RCA_Pb |

|

|

| |||

RCA_Pr |

|

| DAC |

|

| |

|

|

|

| |||

|

|

|

|

|

|

|

Figure 5.19. A TV Encoder that uses the Cyclone II FPGA and the ADV7123.

54