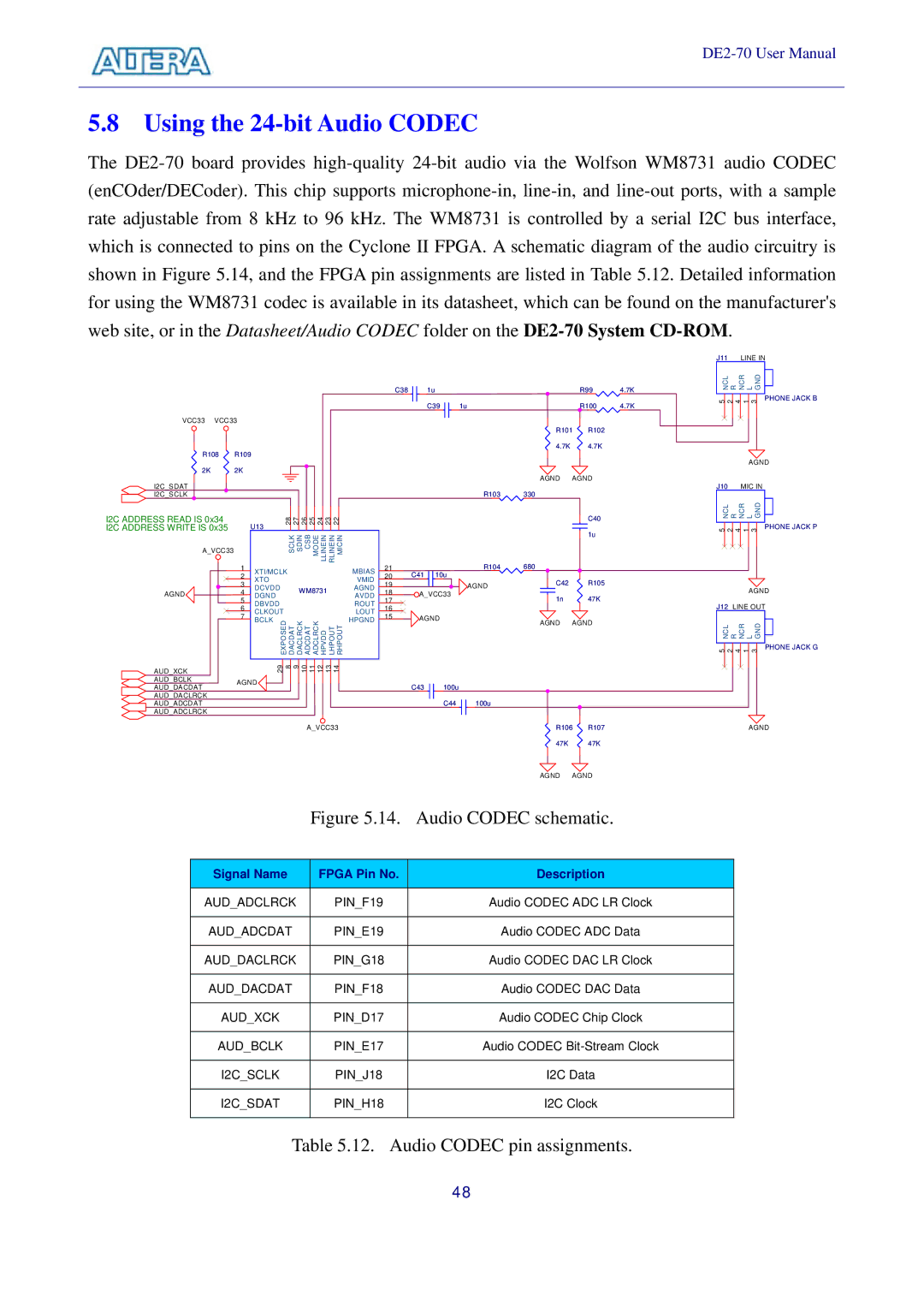

5.8 Using the 24-bit Audio CODEC

The

| C38 | 1u |

|

| R99 | 4.7K |

|

| C39 | 1u |

| R100 | 4.7K |

VCC33 VCC33 |

|

|

|

|

| |

|

|

|

| R101 | R102 |

|

R108 | R109 |

|

| 4.7K | 4.7K |

|

|

|

|

|

| ||

2K | 2K |

|

| AGND AGND |

| |

I2C_SDAT |

|

|

|

| ||

|

|

|

|

|

| |

I2C_SCLK |

|

| R103 | 330 |

|

|

J11 |

| LINE IN | |||||

LCN R RCN L DNG |

|

| |||||

|

| ||||||

|

| ||||||

|

|

|

|

|

|

|

|

5 | 2 | 4 | 1 | 3 |

| PHONE JACK B | |

|

|

|

|

|

| ||

|

|

|

| AGND | |||

J10 |

| MIC IN |

|

| |||

LC | RC | DN |

|

| |||

|

| ||||||

I2C ADDRESS READ IS 0x34 I2C ADDRESS WRITE IS 0x35

A_VCC33

AGND![]()

AUD_XCK

AUD_BCLK

AUD_DACDAT

AUD_DACLRCK

AUD_ADCDAT

AUD_ADCLRCK

| U13 | 28 27 | 26 25 24 23 22 |

| ||||||||

|

|

|

|

|

|

|

|

|

| |||

|

|

|

| LKC IND BS ED INE INE INIC S S C O LLIN LIN M M R | ||||||||

1 | XTI/MCLK |

|

|

|

|

|

| |||||

2 |

|

|

|

|

|

| ||||||

XTO |

|

|

|

|

|

|

|

|

| |||

3 |

|

|

|

|

|

|

|

|

| |||

DCVDD |

|

|

| WM8731 | ||||||||

4 |

|

|

| |||||||||

DGND |

|

|

| |||||||||

5 |

|

|

|

|

|

|

|

|

| |||

DBVDD |

|

|

|

|

|

|

|

|

| |||

6 |

|

|

|

|

|

|

|

|

| |||

CLKOUT |

|

|

|

|

|

|

|

|

| |||

7 |

|

|

|

|

|

|

|

|

| |||

BCLK |

|

|

|

|

|

|

|

|

| |||

|

| DES TA KCLR TA KCLR D TU TU OPX DCA CA DCD CD DVP OPLH OPH E D D A A H R | ||||||||||

|

|

| 8 |

| 9 |

|

|

|

|

|

| |

| 29 |

|

| 10 | 11 | 12 | 13 | 14 |

| |||

|

| |||||||||||

AGND |

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

| A_VCC33 | ||||||

|

|

|

|

|

|

|

| |||||

MBIAS VMID AGND AVDD ROUT LOUT HPGND

|

|

|

|

| C40 |

|

|

|

|

| 1u |

21 | C41 | 10u | R104 | 680 |

|

20 |

| C42 | R105 | ||

19 |

|

| AGND | ||

18 | A_VCC33 |

|

| ||

| 1n | 47K | |||

17 |

| ||||

|

|

| |||

16 |

|

|

|

|

|

15 | AGND |

| AGND AGND | ||

|

| ||||

|

|

|

| ||

| C43 | 100u |

|

|

|

|

| C44 | 100u |

|

|

|

|

|

| R106 | R107 |

|

|

|

| 47K | 47K |

N R N L G |

|

| ||||||

|

|

|

|

|

|

|

| |

5 | 2 | 4 | 1 | 3 |

| PHONE JACK P | ||

|

|

|

|

|

|

| ||

|

|

|

| AGND | ||||

J12 LINE OUT | ||||||||

LCN R RCN L DNG |

|

| ||||||

|

| |||||||

PHONE JACK G | ||||||||

|

|

|

|

|

| |||

5 | 2 | 4 | 1 | 3 |

| |||

|

|

| ||||||

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

| |

|

|

|

| AGND | ||||

|

| AGND AGND |

| Figure 5.14. Audio CODEC schematic. | |

|

|

|

Signal Name | FPGA Pin No. | Description |

|

|

|

AUD_ADCLRCK | PIN_F19 | Audio CODEC ADC LR Clock |

|

|

|

AUD_ADCDAT | PIN_E19 | Audio CODEC ADC Data |

|

|

|

AUD_DACLRCK | PIN_G18 | Audio CODEC DAC LR Clock |

|

|

|

AUD_DACDAT | PIN_F18 | Audio CODEC DAC Data |

|

|

|

AUD_XCK | PIN_D17 | Audio CODEC Chip Clock |

|

|

|

AUD_BCLK | PIN_E17 | Audio CODEC |

|

|

|

I2C_SCLK | PIN_J18 | I2C Data |

|

|

|

I2C_SDAT | PIN_H18 | I2C Clock |

|

|

|

Table 5.12. Audio CODEC pin assignments.

48