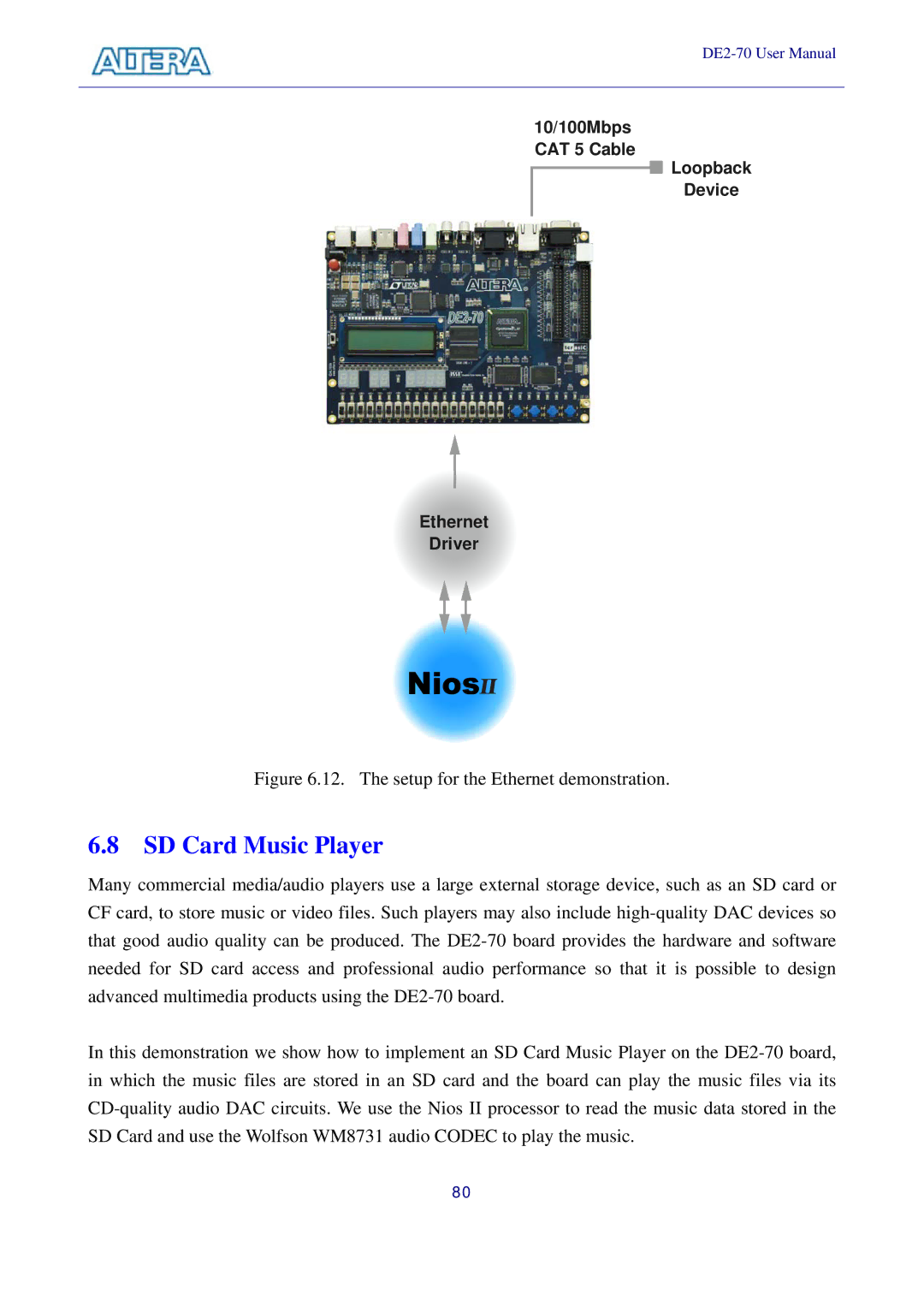

10/100Mbps

CAT 5 Cable

Loopback

Loopback

Device

Ethernet

Driver

Figure 6.12. The setup for the Ethernet demonstration.

6.8 SD Card Music Player

Many commercial media/audio players use a large external storage device, such as an SD card or CF card, to store music or video files. Such players may also include high-quality DAC devices so that good audio quality can be produced. The DE2-70 board provides the hardware and software needed for SD card access and professional audio performance so that it is possible to design advanced multimedia products using the DE2-70 board.

In this demonstration we show how to implement an SD Card Music Player on the DE2-70 board, in which the music files are stored in an SD card and the board can play the music files via its CD-quality audio DAC circuits. We use the Nios II processor to read the music data stored in the SD Card and use the Wolfson WM8731 audio CODEC to play the music.

80

![]() Loopback

Loopback