www.ti.com | Registers |

6.1Peripheral Identification Register (PID)

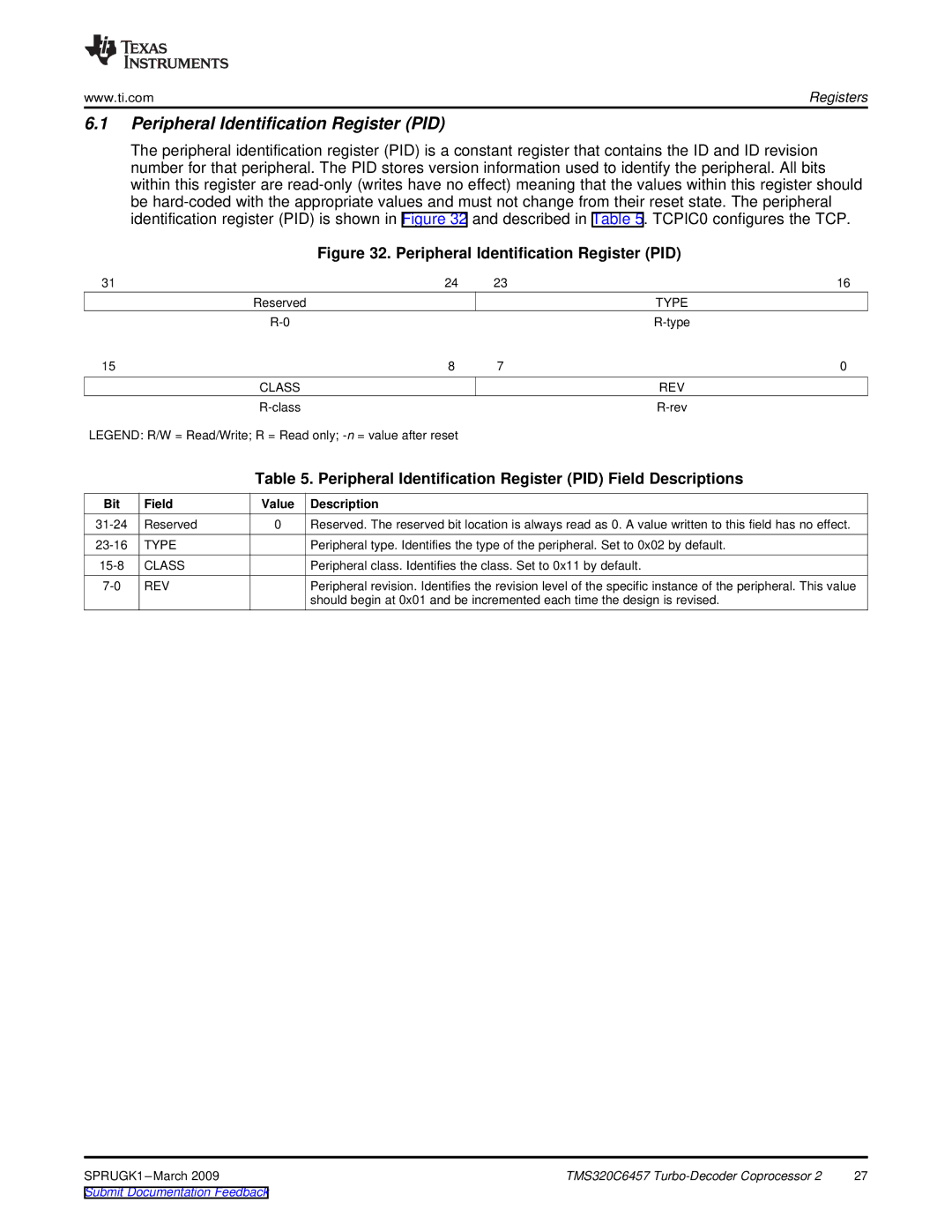

The peripheral identification register (PID) is a constant register that contains the ID and ID revision number for that peripheral. The PID stores version information used to identify the peripheral. All bits within this register are

Figure 32. Peripheral Identification Register (PID)

31 |

|

| 24 | 23 | 16 |

|

| Reserved |

| TYPE |

|

|

|

|

| ||

15 |

|

| 8 | 7 | 0 |

|

| CLASS |

| REV |

|

|

|

|

| ||

LEGEND: R/W = Read/Write; R = Read only; |

|

| |||

|

| Table 5. Peripheral Identification Register (PID) Field Descriptions |

| ||

Bit | Field | Value | Description |

|

|

Reserved | 0 | Reserved. The reserved bit location is always read as 0. A value written to this field has no effect. | |||

TYPE |

| Peripheral type. Identifies the type of the peripheral. Set to 0x02 by default. |

| ||

CLASS |

| Peripheral class. Identifies the class. Set to 0x11 by default. |

| ||

REV |

| Peripheral revision. Identifies the revision level of the specific instance of the peripheral. This value | |||

|

|

| should begin at 0x01 and be incremented each time the design is revised. |

| |

TMS320C6457 | 27 | |

Submit Documentation Feedback |

|

|