www.ti.com | Architecture |

7.1.4.2ENDIAN_EXTR = 0

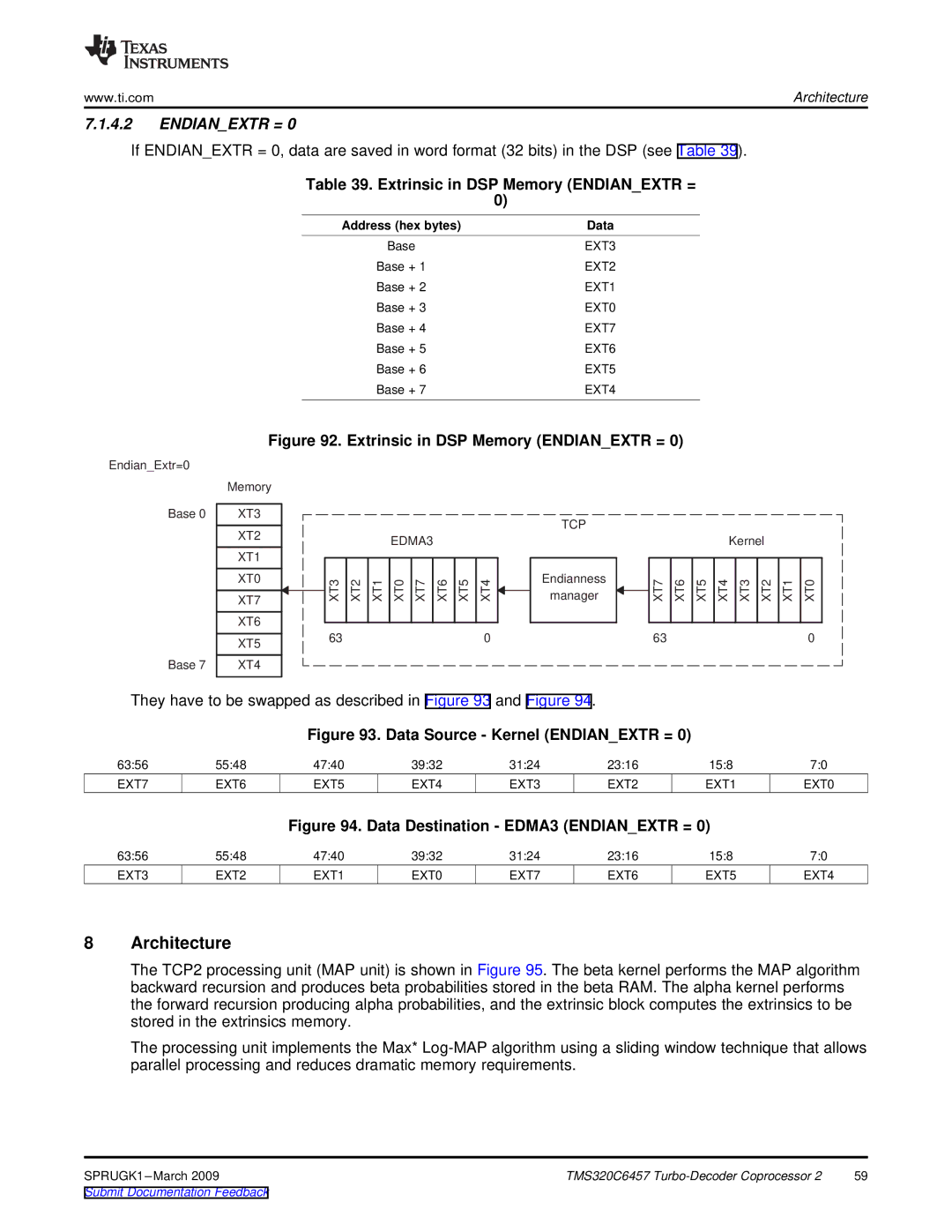

If ENDIAN_EXTR = 0, data are saved in word format (32 bits) in the DSP (see Table 39).

Table 39. Extrinsic in DSP Memory (ENDIAN_EXTR =

0)

Address (hex bytes) | Data |

Base | EXT3 |

Base + 1 | EXT2 |

Base + 2 | EXT1 |

Base + 3 | EXT0 |

Base + 4 | EXT7 |

Base + 5 | EXT6 |

Base + 6 | EXT5 |

Base + 7 | EXT4 |

Figure 92. Extrinsic in DSP Memory (ENDIAN_EXTR = 0)

Endian_Extr=0

Base 0

Base 7

Memory

XT3

XT2

XT1

XT0

XT7

XT6

XT5

XT4

EDMA3

| XT3 | XT2 | XT1 | XT0 | XT7 | XT6 | XT5 | XT4 |

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

| 63 |

|

|

|

|

|

| 0 |

|

TCP

Endianness manager

Kernel

| XT7 | XT6 | XT5 | XT4 | XT3 | XT2 | XT1 | XT0 |

| ||||||||

|

|

|

|

|

|

|

|

|

| 63 |

|

|

|

|

|

| 0 |

They have to be swapped as described in Figure 93 and Figure 94.

Figure 93. Data Source - Kernel (ENDIAN_EXTR = 0)

63:56 | 55:48 | 47:40 | 39:32 | 31:24 | 23:16 | 15:8 | 7:0 |

EXT7 | EXT6 | EXT5 | EXT4 | EXT3 | EXT2 | EXT1 | EXT0 |

Figure 94. Data Destination - EDMA3 (ENDIAN_EXTR = 0)

63:56 | 55:48 | 47:40 | 39:32 | 31:24 | 23:16 | 15:8 | 7:0 |

EXT3 | EXT2 | EXT1 | EXT0 | EXT7 | EXT6 | EXT5 | EXT4 |

8Architecture

The TCP2 processing unit (MAP unit) is shown in Figure 95. The beta kernel performs the MAP algorithm backward recursion and produces beta probabilities stored in the beta RAM. The alpha kernel performs the forward recursion producing alpha probabilities, and the extrinsic block computes the extrinsics to be stored in the extrinsics memory.

The processing unit implements the Max*

TMS320C6457 | 59 |