Endianness | www.ti.com |

The TCP2 is halted (or paused) after processing the ongoing frame. Any current frame processing must complete. Sync vents for the new frame will be hold until TCP_EMUSUSP is released. The TCP2 is restarted from the paused state and begins the next frame operations.

In TCP_STATE = 14, the TCP_EMUSUSP will have no effect. The TCP2 will go to the next state (TCP_STATE=0) and then the emususp will be processed.

In TCP_STATE = 0, the TCP_EMUSUSP will cause the emuack to go active if no EDMA3 transactions are active.

In TCP_STATE = 1, the TCP_EMUSUSP will cause the emuack to go active if no EDMA3 transactions are active. The memory_access error bit will not go active if emuack = 1, and the tcp_int will not trigger if the memories are accessed while emuack = 1.

The emususp_rt signal is not used in the TCP2. Bit[2](RT_SEL) for the emulation register is not included and the bit is reserved.

7Endianness

The endianness manager is responsible for managing the endianness of data when DSP is configured in big endian mode. When the DSP is configured in

This architecture supports both big- and

The TCP2 always works in

For the data represented on the configuration (CFG) data bus, byte endianness is not an issue. The endianness manager has no effect on

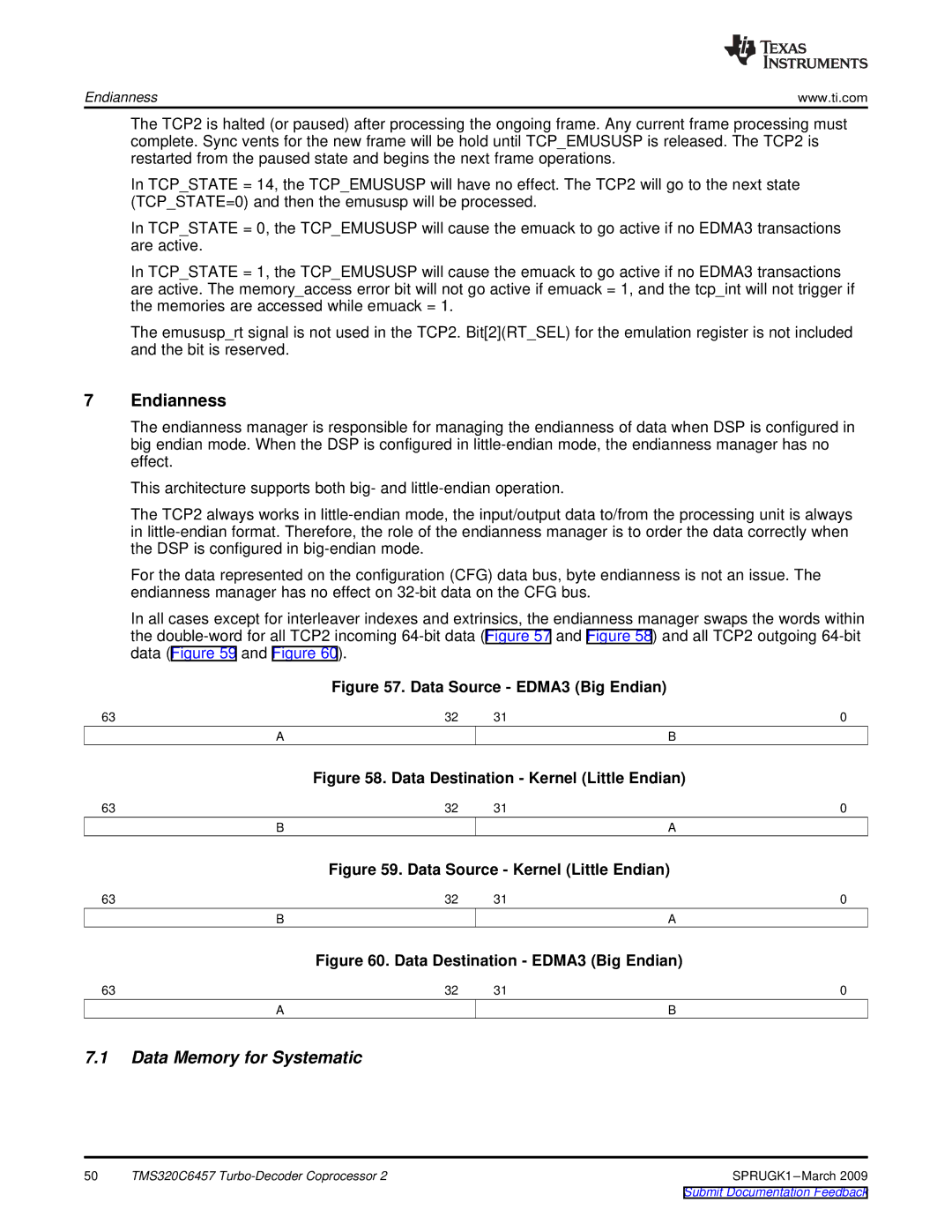

In all cases except for interleaver indexes and extrinsics, the endianness manager swaps the words within the

Figure 57. Data Source - EDMA3 (Big Endian)

63 | 32 | 31 | 0 |

| A |

| B |

Figure 58. Data Destination - Kernel (Little Endian)

63 | 32 | 31 | 0 |

| B |

| A |

Figure 59. Data Source - Kernel (Little Endian)

63 | 32 | 31 | 0 |

| B |

| A |

Figure 60. Data Destination - EDMA3 (Big Endian)

63 | 32 | 31 | 0 |

| A |

| B |

7.1Data Memory for Systematic

50 | TMS320C6457 | |

|

| Submit Documentation Feedback |