www.ti.com | Registers |

6.9TCP2 Input Configuration Register 6 (TCPIC6)

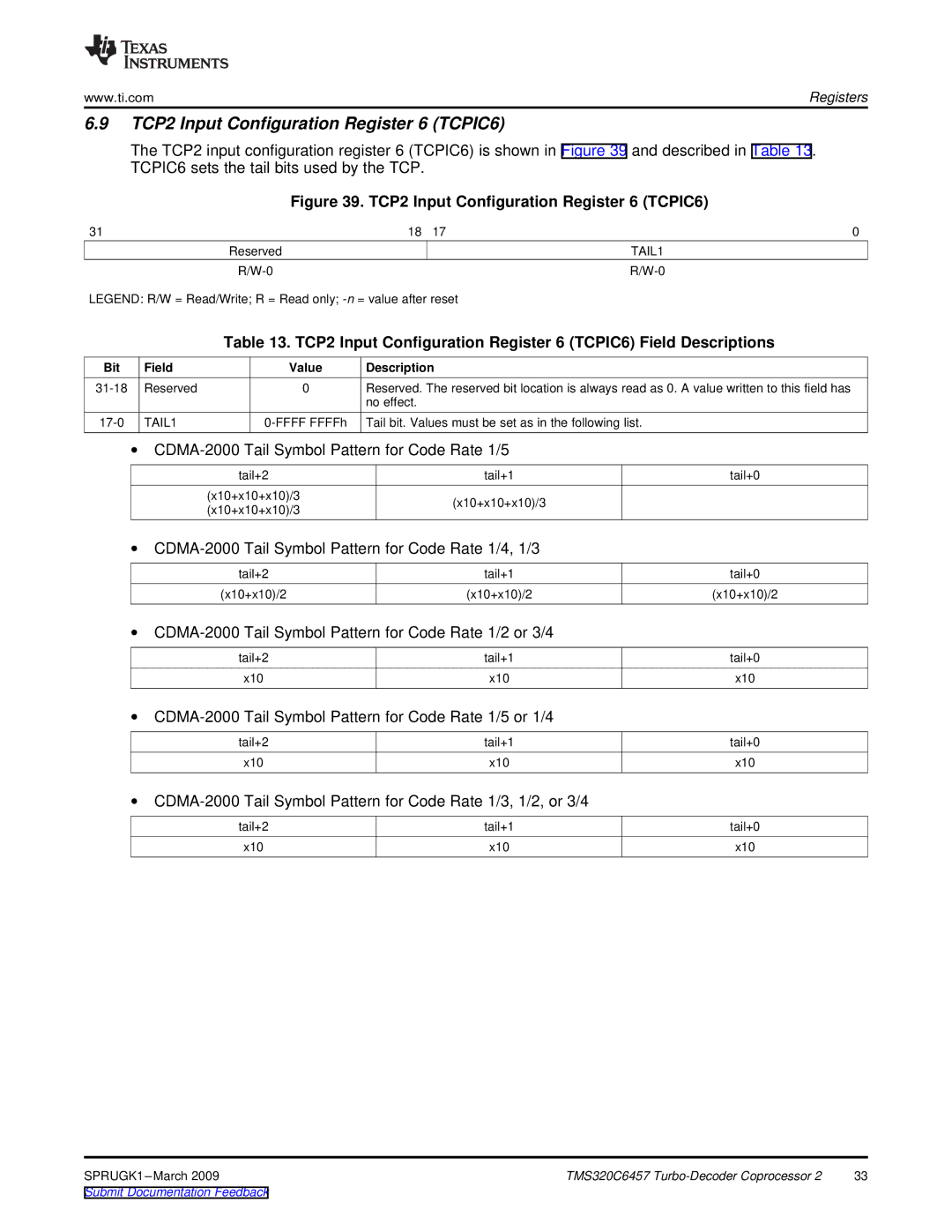

The TCP2 input configuration register 6 (TCPIC6) is shown in Figure 39 and described in Table 13. TCPIC6 sets the tail bits used by the TCP.

Figure 39. TCP2 Input Configuration Register 6 (TCPIC6)

31 | 18 | 17 | 0 |

| Reserved |

| TAIL1 |

|

|

LEGEND: R/W = Read/Write; R = Read only;

Table 13. TCP2 Input Configuration Register 6 (TCPIC6) Field Descriptions

Bit | Field | Value | Description |

Reserved | 0 | Reserved. The reserved bit location is always read as 0. A value written to this field has | |

|

|

| no effect. |

TAIL1 | Tail bit. Values must be set as in the following list. |

∙

tail+2 | tail+1 | tail+0 |

(x10+x10+x10)/3

(x10+x10+x10)/3

(x10+x10+x10)/3

∙

tail+2 | tail+1 | tail+0 |

(x10+x10)/2 | (x10+x10)/2 | (x10+x10)/2 |

∙

tail+2 | tail+1 | tail+0 |

x10 | x10 | x10 |

∙

tail+2 | tail+1 | tail+0 |

x10 | x10 | x10 |

∙

tail+2 | tail+1 | tail+0 |

x10 | x10 | x10 |

TMS320C6457 | 33 |