www.ti.com | Registers |

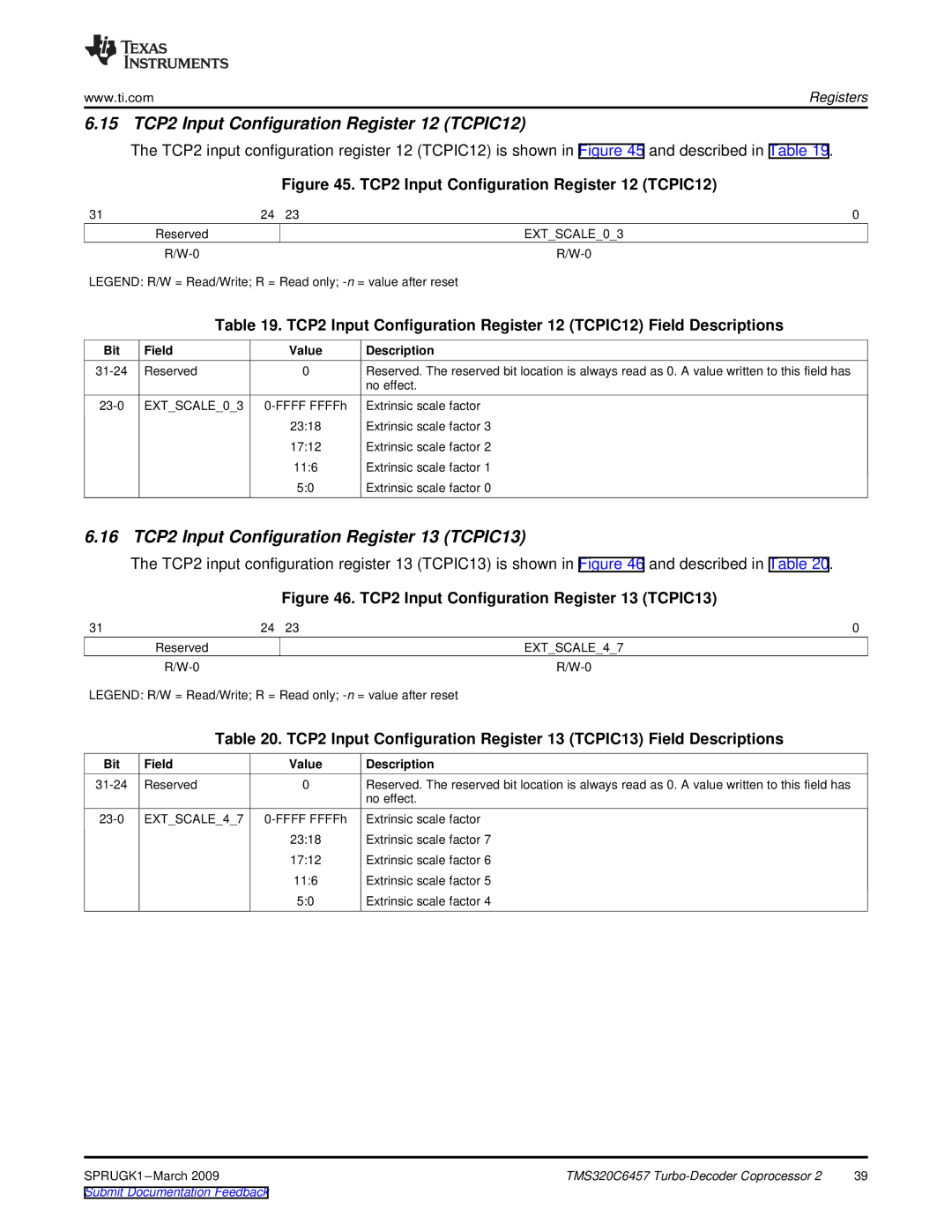

6.15 TCP2 Input Configuration Register 12 (TCPIC12)

The TCP2 input configuration register 12 (TCPIC12) is shown in Figure 45 and described in Table 19.

Figure 45. TCP2 Input Configuration Register 12 (TCPIC12)

31 | 24 | 23 | 0 |

| Reserved |

| EXT_SCALE_0_3 |

|

|

LEGEND: R/W = Read/Write; R = Read only;

Table 19. TCP2 Input Configuration Register 12 (TCPIC12) Field Descriptions

Bit | Field | Value | Description |

Reserved | 0 | Reserved. The reserved bit location is always read as 0. A value written to this field has | |

|

|

| no effect. |

EXT_SCALE_0_3 | Extrinsic scale factor | ||

|

| 23:18 | Extrinsic scale factor 3 |

|

| 17:12 | Extrinsic scale factor 2 |

|

| 11:6 | Extrinsic scale factor 1 |

|

| 5:0 | Extrinsic scale factor 0 |

6.16 TCP2 Input Configuration Register 13 (TCPIC13)

The TCP2 input configuration register 13 (TCPIC13) is shown in Figure 46 and described in Table 20.

Figure 46. TCP2 Input Configuration Register 13 (TCPIC13)

31 | 24 | 23 | 0 |

| Reserved |

| EXT_SCALE_4_7 |

|

|

LEGEND: R/W = Read/Write; R = Read only;

Table 20. TCP2 Input Configuration Register 13 (TCPIC13) Field Descriptions

Bit | Field | Value | Description |

Reserved | 0 | Reserved. The reserved bit location is always read as 0. A value written to this field has | |

|

|

| no effect. |

EXT_SCALE_4_7 | Extrinsic scale factor | ||

|

| 23:18 | Extrinsic scale factor 7 |

|

| 17:12 | Extrinsic scale factor 6 |

|

| 11:6 | Extrinsic scale factor 5 |

|

| 5:0 | Extrinsic scale factor 4 |

TMS320C6457 | 39 | |

Submit Documentation Feedback |

|

|