www.ti.com |

|

|

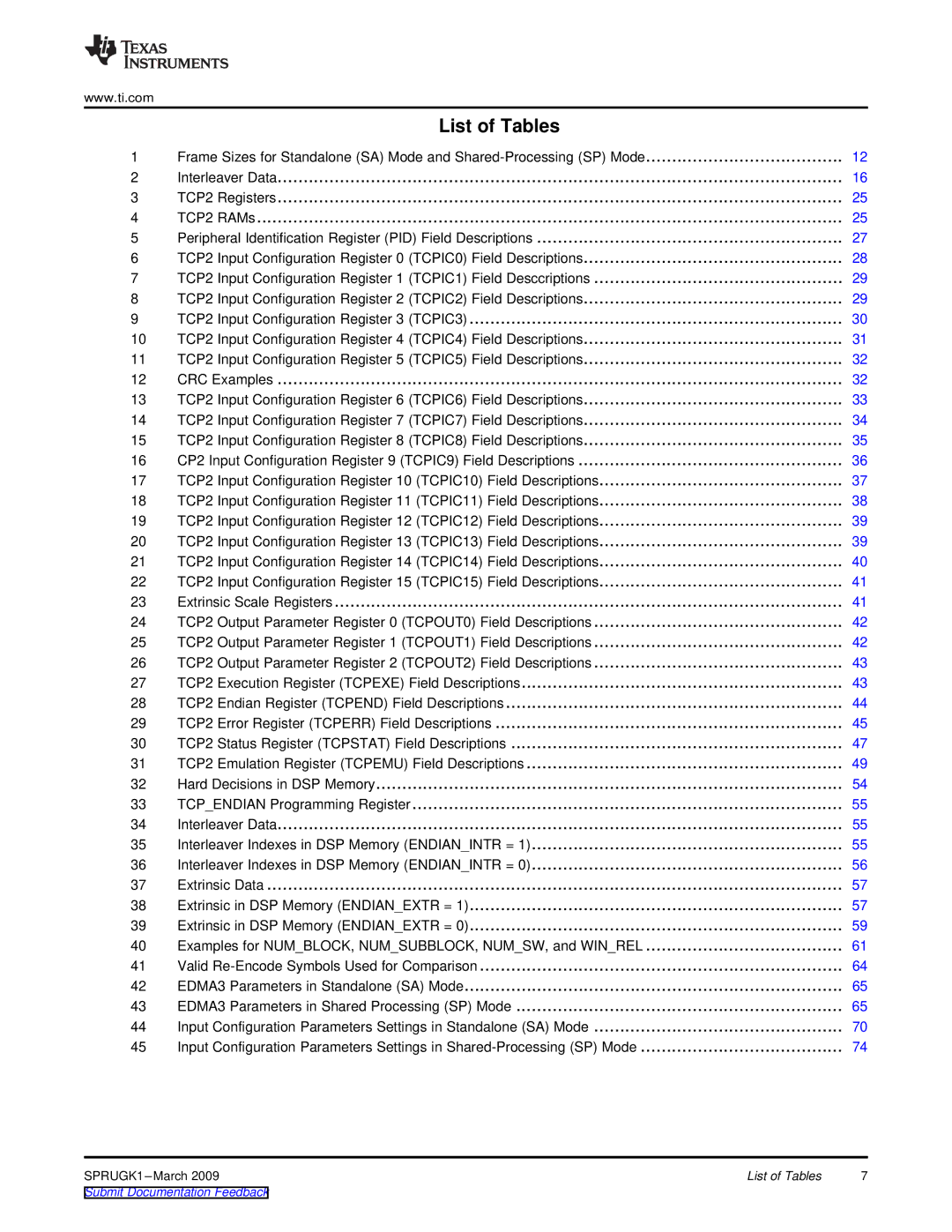

| List of Tables |

|

1 | Frame Sizes for Standalone (SA) Mode and | 12 |

2 | Interleaver Data | 16 |

3 | TCP2 Registers | 25 |

4 | TCP2 RAMs | 25 |

5 | Peripheral Identification Register (PID) Field Descriptions | 27 |

6 | TCP2 Input Configuration Register 0 (TCPIC0) Field Descriptions | 28 |

7 | TCP2 Input Configuration Register 1 (TCPIC1) Field Desccriptions | 29 |

8 | TCP2 Input Configuration Register 2 (TCPIC2) Field Descriptions | 29 |

9 | TCP2 Input Configuration Register 3 (TCPIC3) | 30 |

10 | TCP2 Input Configuration Register 4 (TCPIC4) Field Descriptions | 31 |

11 | TCP2 Input Configuration Register 5 (TCPIC5) Field Descriptions | 32 |

12 | CRC Examples | 32 |

13 | TCP2 Input Configuration Register 6 (TCPIC6) Field Descriptions | 33 |

14 | TCP2 Input Configuration Register 7 (TCPIC7) Field Descriptions | 34 |

15 | TCP2 Input Configuration Register 8 (TCPIC8) Field Descriptions | 35 |

16 | CP2 Input Configuration Register 9 (TCPIC9) Field Descriptions | 36 |

17 | TCP2 Input Configuration Register 10 (TCPIC10) Field Descriptions | 37 |

18 | TCP2 Input Configuration Register 11 (TCPIC11) Field Descriptions | 38 |

19 | TCP2 Input Configuration Register 12 (TCPIC12) Field Descriptions | 39 |

20 | TCP2 Input Configuration Register 13 (TCPIC13) Field Descriptions | 39 |

21 | TCP2 Input Configuration Register 14 (TCPIC14) Field Descriptions | 40 |

22 | TCP2 Input Configuration Register 15 (TCPIC15) Field Descriptions | 41 |

23 | Extrinsic Scale Registers | 41 |

24 | TCP2 Output Parameter Register 0 (TCPOUT0) Field Descriptions | 42 |

25 | TCP2 Output Parameter Register 1 (TCPOUT1) Field Descriptions | 42 |

26 | TCP2 Output Parameter Register 2 (TCPOUT2) Field Descriptions | 43 |

27 | TCP2 Execution Register (TCPEXE) Field Descriptions | 43 |

28 | TCP2 Endian Register (TCPEND) Field Descriptions | 44 |

29 | TCP2 Error Register (TCPERR) Field Descriptions | 45 |

30 | TCP2 Status Register (TCPSTAT) Field Descriptions | 47 |

31 | TCP2 Emulation Register (TCPEMU) Field Descriptions | 49 |

32 | Hard Decisions in DSP Memory | 54 |

33 | TCP_ENDIAN Programming Register | 55 |

34 | Interleaver Data | 55 |

35 | Interleaver Indexes in DSP Memory (ENDIAN_INTR = 1) | 55 |

36 | Interleaver Indexes in DSP Memory (ENDIAN_INTR = 0) | 56 |

37 | Extrinsic Data | 57 |

38 | Extrinsic in DSP Memory (ENDIAN_EXTR = 1) | 57 |

39 | Extrinsic in DSP Memory (ENDIAN_EXTR = 0) | 59 |

40 | Examples for NUM_BLOCK, NUM_SUBBLOCK, NUM_SW, and WIN_REL | 61 |

41 | Valid | 64 |

42 | EDMA3 Parameters in Standalone (SA) Mode | 65 |

43 | EDMA3 Parameters in Shared Processing (SP) Mode | 65 |

44 | Input Configuration Parameters Settings in Standalone (SA) Mode | 70 |

45 | Input Configuration Parameters Settings in | 74 |

List of Tables | 7 |