www.ti.com | Registers |

6.13 TCP2 Input Configuration Register 10 (TCPIC10)

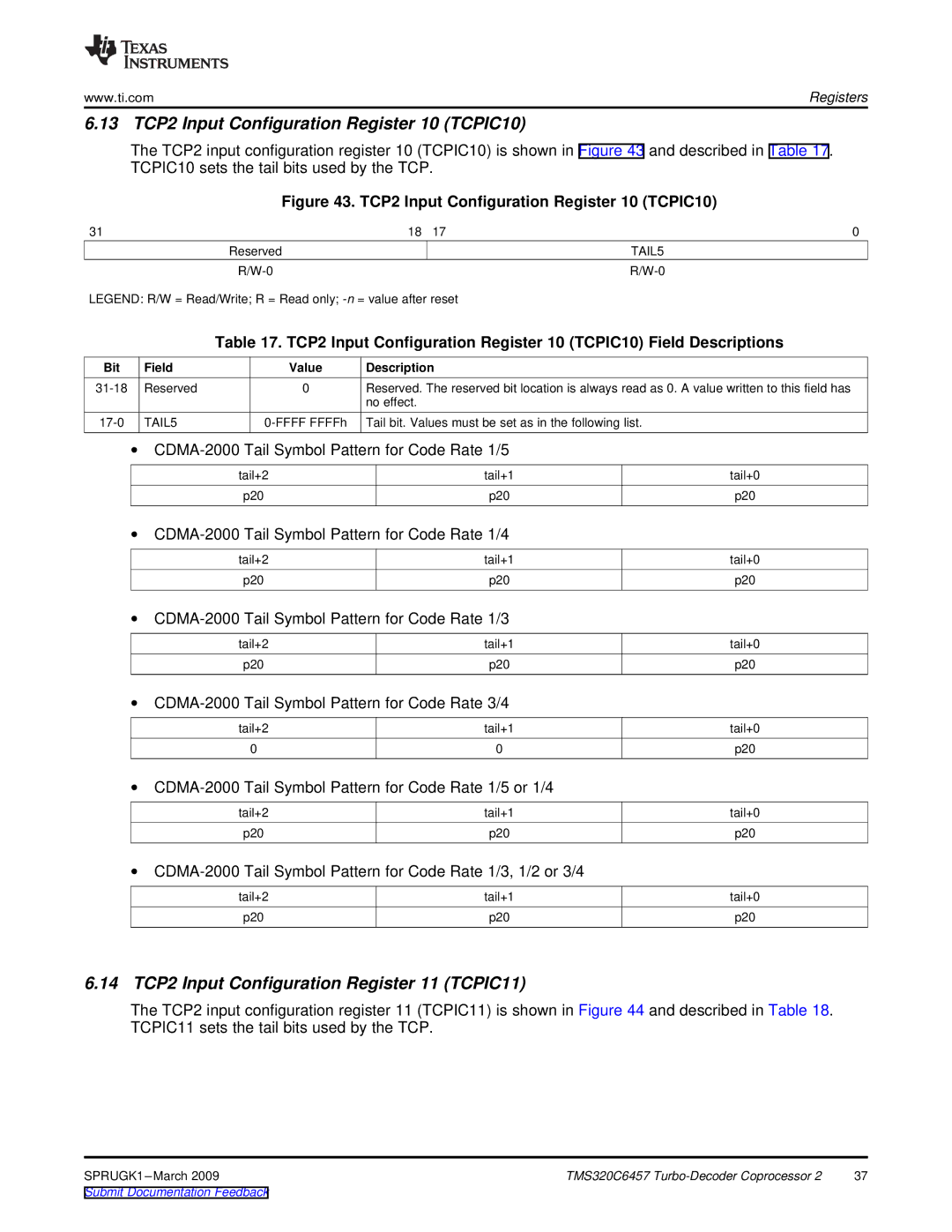

The TCP2 input configuration register 10 (TCPIC10) is shown in Figure 43 and described in Table 17. TCPIC10 sets the tail bits used by the TCP.

Figure 43. TCP2 Input Configuration Register 10 (TCPIC10)

31 | 18 | 17 | 0 |

| Reserved |

| TAIL5 |

|

|

LEGEND: R/W = Read/Write; R = Read only;

Table 17. TCP2 Input Configuration Register 10 (TCPIC10) Field Descriptions

Bit | Field | Value | Description |

Reserved | 0 | Reserved. The reserved bit location is always read as 0. A value written to this field has | |

|

|

| no effect. |

TAIL5 | Tail bit. Values must be set as in the following list. |

∙

tail+2 | tail+1 | tail+0 |

p20 | p20 | p20 |

∙

tail+2 | tail+1 | tail+0 |

p20 | p20 | p20 |

∙

tail+2 | tail+1 | tail+0 |

p20 | p20 | p20 |

∙

tail+2 | tail+1 | tail+0 |

0 | 0 | p20 |

∙

tail+2 | tail+1 | tail+0 |

p20 | p20 | p20 |

∙

tail+2 | tail+1 | tail+0 |

p20 | p20 | p20 |

6.14 TCP2 Input Configuration Register 11 (TCPIC11)

The TCP2 input configuration register 11 (TCPIC11) is shown in Figure 44 and described in Table 18. TCPIC11 sets the tail bits used by the TCP.

TMS320C6457 | 37 |