www.ti.com | Registers |

6.24 TCP2 Error Register (TCPERR)

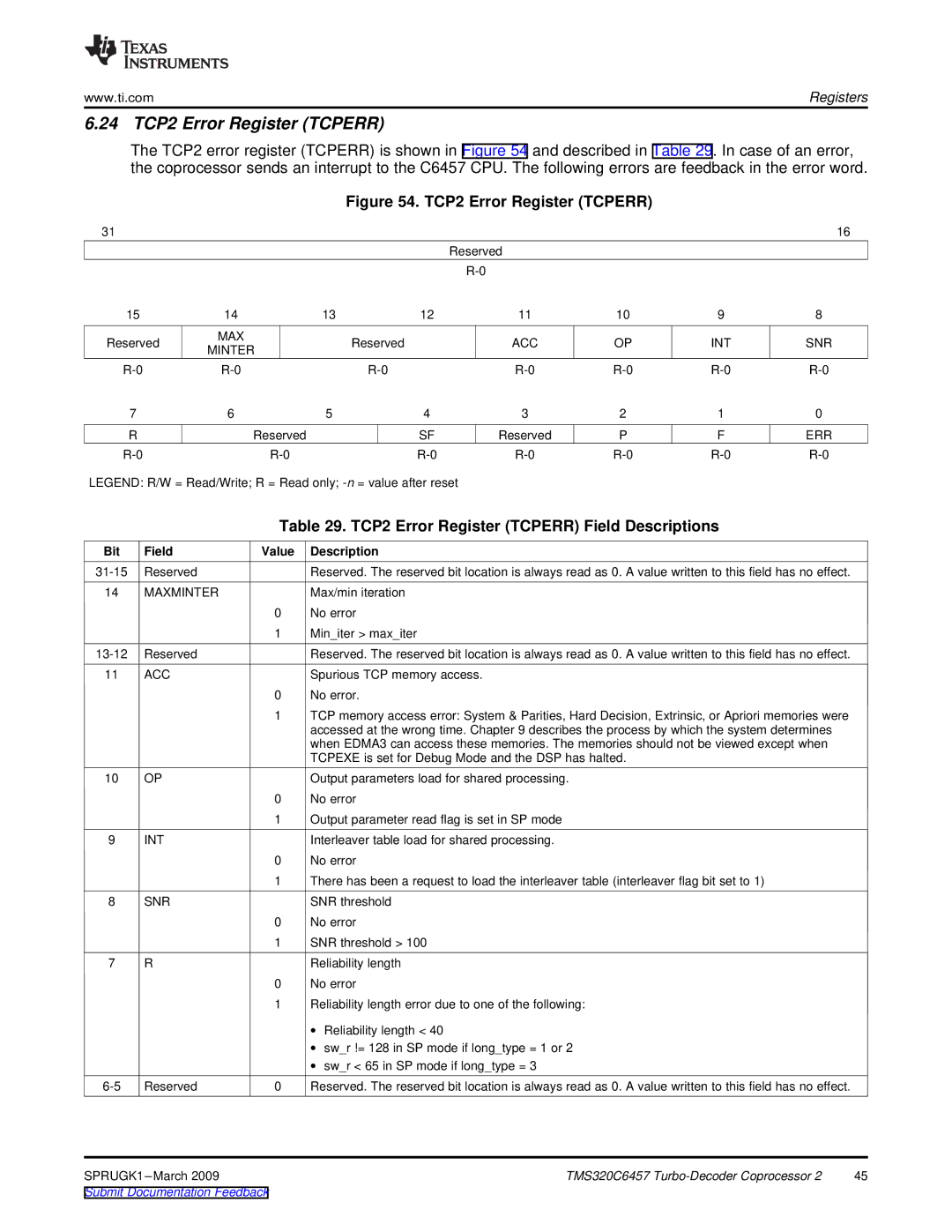

The TCP2 error register (TCPERR) is shown in Figure 54 and described in Table 29. In case of an error, the coprocessor sends an interrupt to the C6457 CPU. The following errors are feedback in the error word.

Figure 54. TCP2 Error Register (TCPERR)

31 |

|

|

|

|

|

|

| 16 |

|

|

|

| Reserved |

|

|

| |

|

|

|

|

|

|

|

| |

15 |

| 14 | 13 | 12 | 11 | 10 | 9 | 8 |

Reserved | MAX | Reserved |

| ACC | OP | INT | SNR | |

MINTER |

| |||||||

|

|

|

|

|

|

|

| |

|

| |||||||

7 |

| 6 | 5 | 4 | 3 | 2 | 1 | 0 |

R |

| Reserved |

| SF | Reserved | P | F | ERR |

|

| |||||||

LEGEND: R/W = Read/Write; R = Read only; |

|

|

|

| ||||

|

| Table 29. TCP2 Error Register (TCPERR) Field Descriptions |

| |||||

Bit | Field | Value | Description |

|

|

|

|

|

Reserved |

| Reserved. The reserved bit location is always read as 0. A value written to this field has no effect. | ||||||

14 | MAXMINTER | Max/min iteration |

|

|

|

|

| |

|

| 0 | No error |

|

|

|

|

|

|

| 1 | Min_iter > max_iter |

|

|

|

|

|

Reserved |

| Reserved. The reserved bit location is always read as 0. A value written to this field has no effect. | ||||||

11 | ACC |

| Spurious TCP memory access. |

|

|

|

| |

|

| 0 | No error. |

|

|

|

|

|

|

| 1 | TCP memory access error: System & Parities, Hard Decision, Extrinsic, or Apriori memories were | |||||

|

|

| accessed at the wrong time. Chapter 9 describes the process by which the system determines | |||||

|

|

| when EDMA3 can access these memories. The memories should not be viewed except when | |||||

|

|

| TCPEXE is set for Debug Mode and the DSP has halted. |

|

| |||

10 | OP |

| Output parameters load for shared processing. |

|

|

| ||

|

| 0 | No error |

|

|

|

|

|

|

| 1 | Output parameter read flag is set in SP mode |

|

|

| ||

9 | INT |

| Interleaver table load for shared processing. |

|

|

| ||

|

| 0 | No error |

|

|

|

|

|

|

| 1 | There has been a request to load the interleaver table (interleaver flag bit set to 1) |

| ||||

8 | SNR |

| SNR threshold |

|

|

|

|

|

|

| 0 | No error |

|

|

|

|

|

|

| 1 | SNR threshold > 100 |

|

|

|

| |

7 | R |

| Reliability length |

|

|

|

|

|

|

| 0 | No error |

|

|

|

|

|

|

| 1 | Reliability length error due to one of the following: |

|

|

| ||

|

|

| ∙ Reliability length < 40 |

|

|

|

| |

|

|

| ∙ sw_r != 128 in SP mode if long_type = 1 or 2 |

|

|

| ||

|

|

| ∙ sw_r < 65 in SP mode if long_type = 3 |

|

|

| ||

Reserved | 0 | Reserved. The reserved bit location is always read as 0. A value written to this field has no effect. | ||||||

TMS320C6457 | 45 | |

Submit Documentation Feedback |

|

|